1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZZyVl51t

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

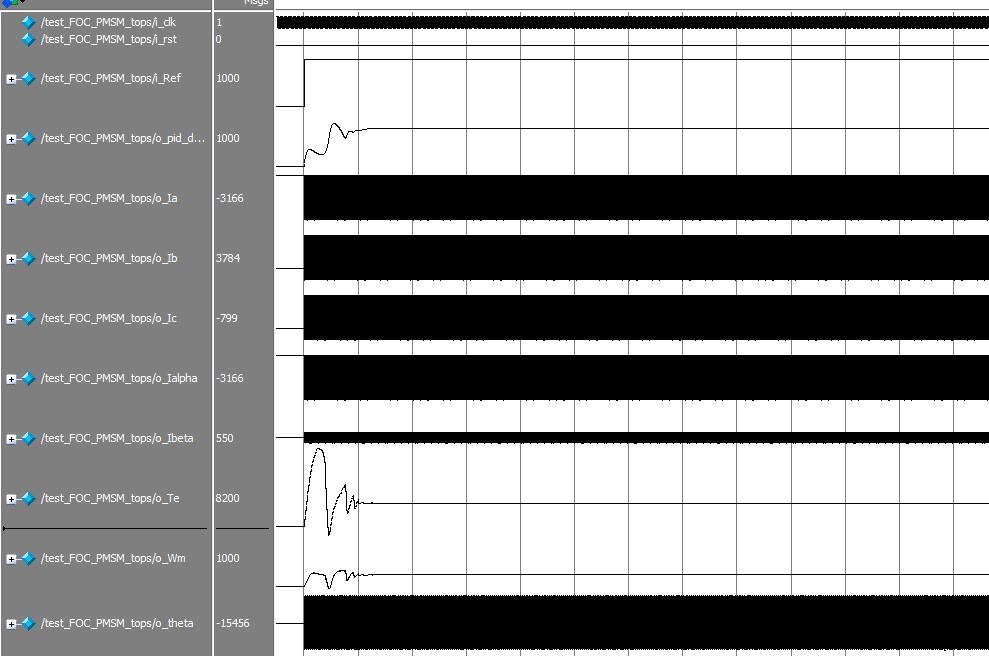

2.部分仿真图预览

3.算法概述

FOC控制的其实是电机的电磁场方向。转子的转子力矩正比于定子的磁场向量与转子磁场矢量的矢量积。由矢量的关系可知,若使电机的转矩时刻保持最大,则定子磁场向量应与转子磁场向量相互垂直。又因为磁场的大小与方向与电流的大小与方向有着直接的关系,所以在用FOC控制算法控制BLDC时的关键就是控制三相输入的电流大小与方向。而控制电流产生定子磁场与转子磁场垂直的关键在:控制稳定的三相输入电压及其电流向量,并且我们得知道转子的实时位置。

4.部分源码

...................................................................

PID_tops PID_tops_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_kp (16'b0001_1111_1111_1111),

.i_ki (16'b0000_0000_0010_0011),

.i_kd (16'b0000_0000_0000_0001),

.i_din (err1),

.o_dout (o_pid_dout),

//test port

.o_doutp (),

.o_douti (),

.o_doutd ()

);

wire signed[15:0]o_Id;

wire signed[15:0]o_Iq;

wire signed[15:0]err11;

wire signed[15:0]err12;

assign err11 = o_pid_dout-o_Id;

assign err12 = 0-o_Iq;

wire signed[15:0]o_pid_dout1;

wire signed[15:0]o_pid_dout2;

PID_tops PID_tops_u1(

.i_clk (i_clk),

.i_rst (i_rst),

.i_kp (16'b0001_1111_1111_1111),

.i_ki (16'b0000_0000_0010_0011),

.i_kd (16'b0000_0000_0000_0001),

.i_din (err11),

.o_dout (o_pid_dout1),

//test port

.o_doutp (),

.o_douti (),

.o_doutd ()

);

PID_tops PID_tops_u2(

.i_clk (i_clk),

.i_rst (i_rst),

.i_kp (16'b0001_1111_1111_1111),

.i_ki (16'b0000_0000_0010_0011),

.i_kd (16'b0000_0000_0000_0001),

.i_din (err12),

.o_dout (o_pid_dout2),

//test port

.o_doutp (),

.o_douti (),

.o_doutd ()

);

//

//INV PARK

wire signed[15:0]o_Uaref;

wire signed[15:0]o_Ubref;

INVPARK INVPARK_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_D (o_pid_dout1),

.i_Q (o_pid_dout2),

.i_theta (o_theta),

.o_alpha (o_Uaref),

.o_beta (o_Ubref)

);

//

//SVPWM

wire w_PWM1;

wire w_PWM2;

wire w_PWM3;

wire w_PWM4;

wire w_PWM5;

wire w_PWM6;

SVPWM SVPWM_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_Uaref(o_Uaref),

.i_Ubref(o_Ubref),

.o_PWM1 (w_PWM1),

.o_PWM2 (w_PWM2),

.o_PWM3 (w_PWM3),

.o_PWM4 (w_PWM4),

.o_PWM5 (w_PWM5),

.o_PWM6 (w_PWM6)

);

//

//IGBT+PMSM

IGBT_PMSM_simple IGBT_PMSM_simple_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_PWM1 (w_PWM1),

.i_PWM2 (w_PWM2),

.i_PWM3 (w_PWM3),

.i_PWM4 (w_PWM4),

.i_PWM5 (w_PWM5),

.i_PWM6 (w_PWM6),

.i_pid (o_pid_dout),

.i_Te (16'd100),

.o_Ia (o_Ia),

.o_Ib (o_Ib),

.o_Ic (o_Ic),

.o_Te (o_Te),

.o_Wm (o_Wm),

.o_theta(o_theta)

);

//

//CLARK

CLARK CLARK_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_Ia (o_Ia),

.i_Ib (o_Ib),

.o_Id (o_Ialpha),

.o_Iq (o_Ibeta)

);

//

//PARK

PARK PARK_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_d (o_Ialpha),

.i_q (o_Ibeta),

.i_theta (o_theta),

.o_ID (o_Id),

.o_IQ (o_Iq)

);

endmodule

08_060_m