1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJaZmpxy

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

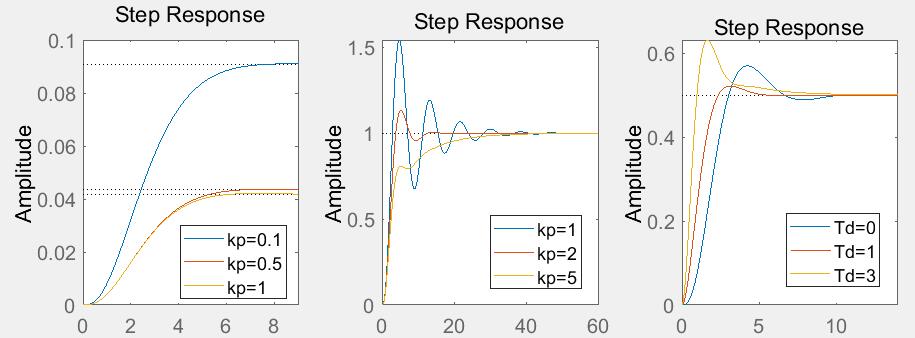

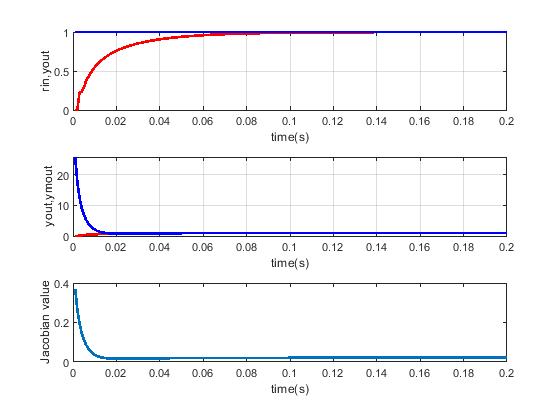

2.部分仿真图预览

3.算法概述

PID控制器以其结构简单、稳定性好、工作可靠、调整方便而成为工业控制的主要技术之一。当控制对象不能通过有效的测量手段来获得系统参数时,最适合用PID控制技术。PID控制,实际中也有PI和PD控制。PID控制器就是根据系统的误差,利用比例、积分、微分计算出控制量进行控制的。

4.部分源码

.......................................................................

M=0;

switch M

case 0

case 1 %Only PID Control

kp(k)=kp0;

ki(k)=ki0;

kd(k)=kd0;

end

du(k)=kp(k)*xc(1)+kd(k)*xc(2)+ki(k)*xc(3);

u(k)=u_1+du(k);

%Return of parameters

x(1)=du(k);

x(2)=yout(k);

x(3)=y_1;

u_1=u(k);

y_1=yout(k);

ci_3=ci_2;

ci_2=ci_1;

ci_1=ci;

bi_3=bi_2;

bi_2=bi_1;

bi_1=bi;

w_3=w_2;

w_2=w_1;

w_1=w;

xc(1)=error(k)-error_1; %Calculating P

xc(2)=error(k)-2*error_1+error_2; %Calculating D

xc(3)=error(k); %Calculating I

error_2=error_1;

error_1=error(k);

kp_1=kp(k);

kd_1=kd(k);

ki_1=ki(k);

end

figure(1);

subplot(311);

plot(time,yout,'r','linewidth',2);

hold on;

plot(time,rin,'b','linewidth',2);

grid on;

xlabel('time(s)');

ylabel('rin,yout');

subplot(312);

plot(time,yout,'r','linewidth',2);

hold on

plot(time,ymout,'b','linewidth',2);

grid on;

xlabel('time(s)');

ylabel('yout,ymout');

subplot(313);

plot(time,dyout,'linewidth',2);

xlabel('time(s)');

ylabel('Jacobian value');

figure(2);

subplot(311);

plot(time,kp,'g','linewidth',2);

xlabel('time(s)','linewidth',2);

ylabel('kp');

subplot(312);

plot(time,ki,'g','linewidth',2);

xlabel('time(s)');

ylabel('ki');

subplot(313);

plot(time,kd,'g','linewidth',2);

xlabel('time(s)');

ylabel('kd');

disp('kp整定值');round(1e3*kp(end))

disp('ki整定值');round(1e3*ki(end))

disp('kd整定值');round(1e3*kd(end))

----------------------------------------------------------------

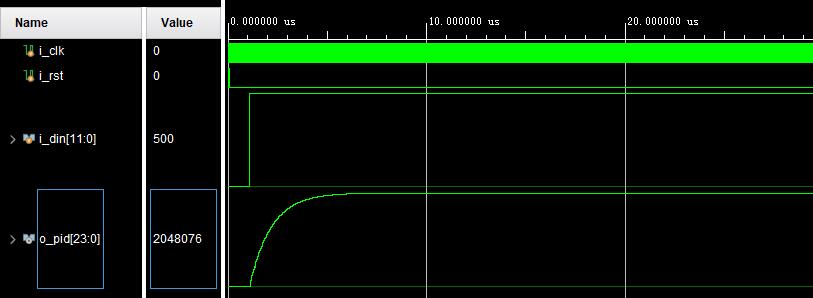

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/03/19 20:45:54

// Design Name:

// Module Name: tops

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

.............................................................

//这个参数是MATLAB RBF参数整定得到的结果,运行main2.m得到参数值

parameter Kp = 12'd75;

parameter Kd = 12'd51;

parameter Ki = 12'd150;

input i_clk;

input i_rst;

input signed[11:0]i_din;

output signed[23:0]o_pid;

reg signed[11:0]o_error;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

o_error <= 12'd0;

end

else begin

o_error <= i_din-o_pid[23:12];

end

end

.....................................................................

08_038_m