1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZpaXl5tt

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

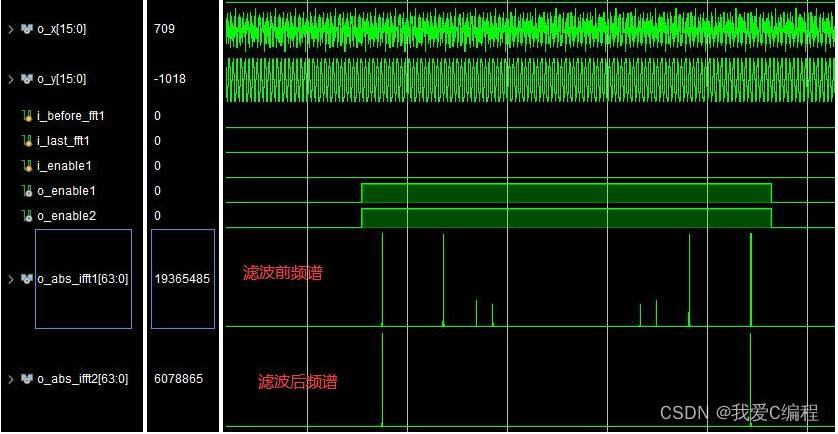

2.部分仿真图预览

3.算法概述

基于FPGA(Field-Programmable Gate Array,现场可编程门阵列)的数字低通滤波器实现和FPGA频谱分析是数字信号处理领域的重要应用,广泛应用于通信、音频处理、图像处理等多个行业。数字低通滤波器旨在允许低频信号通过而衰减高频信号,是信号处理中基础且重要的组件之一。其设计通常基于时域采样定理和滤波器设计理论,常见的实现方法有IIR(无限脉冲响应)滤波器和FIR(有限脉冲响应)滤波器。

4.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/05/27 21:38:45

// Design Name:

// Module Name: test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module test();

reg i_clk;

reg i_rst;

wire signed[15:0]o_x;

wire signed[15:0]o_y;

reg i_before_fft1;

reg i_last_fft1;

reg i_enable1;

wire o_enable1;

wire o_enable2;

wire signed[63:0]o_abs_ifft1;

wire signed[63:0]o_abs_ifft2;

tops tops_U(

.i_clk (i_clk),

.i_rst (i_rst),

.o_x (o_x),

.o_y (o_y),

.i_before_fft1 (i_before_fft1),

.i_last_fft1 (i_last_fft1),

.i_enable1 (i_enable1),

.o_enable1 (o_enable1),

.o_enable2 (o_enable2),

.o_abs_ifft1 (o_abs_ifft1),

.o_abs_ifft2 (o_abs_ifft2)

);

initial

begin

i_clk=1'b1;

i_rst=1'b1;

#100

i_rst = 1'b0;

end

always #5 i_clk=~i_clk;

reg [19:0]cnts2;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

cnts2 <= 20'd0;

i_before_fft1<=1'b0;

i_enable1 <=1'b0;

i_last_fft1 <=1'b0;

end

else begin

if(cnts2==20'd25000)

cnts2 <= cnts2;

else

cnts2 <= cnts2 + 20'd1;

if(cnts2==20'd0)

begin

i_before_fft1<=1'b1;

i_enable1 <=1'b0;

i_last_fft1 <=1'b0;

end

if(cnts2==20'd1)

begin

i_before_fft1<=1'b1;

i_enable1 <=1'b0;

i_last_fft1 <=1'b0;

end

if(cnts2==20'd2)

begin

i_before_fft1<=1'b1;

i_enable1 <=1'b0;

i_last_fft1 <=1'b0;

end

if(cnts2==20'd3)

begin

i_before_fft1<=1'b1;

i_enable1 <=1'b0;

i_last_fft1 <=1'b0;

end

if(cnts2==20'd4)

begin

i_before_fft1<=1'b0;

i_enable1 <=1'b0;

i_last_fft1 <=1'b0;

end

if(cnts2>=20'd5 & cnts2<=20'd4+2047)

begin

i_before_fft1<=1'b0;

i_enable1 <=1'b1;

i_last_fft1 <=1'b0;

end

if(cnts2==20'd4+2048)

begin

i_before_fft1<=1'b0;

i_enable1 <=1'b1;

i_last_fft1 <=1'b1;

end

if(cnts2>20'd4+2048)

begin

i_before_fft1<=1'b0;

i_enable1 <=1'b0;

i_last_fft1 <=1'b0;

end

end

end

endmodule

00_065m

---