1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJeVmJlx

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

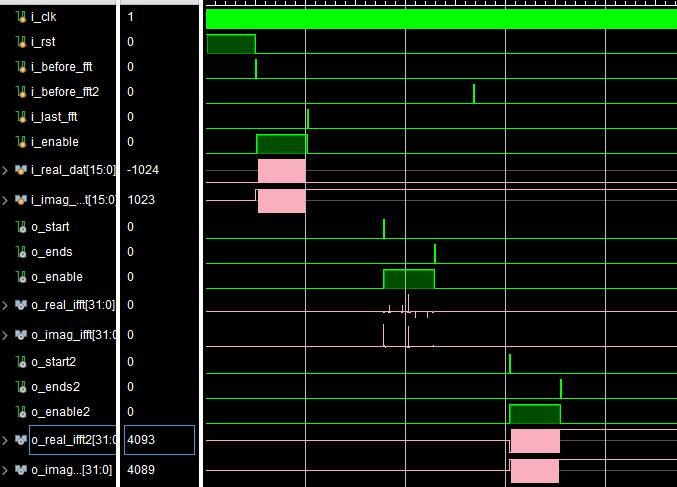

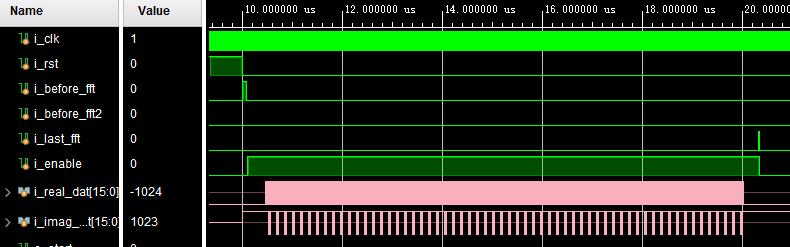

2.部分仿真图预览

3.算法概述

FFT的基本思想是把原始的N点序列,依次分解成一系列的短序列。充分利用DFT计算式中指数因子 所具有的对称性质和周期性质,进而求出这些短序列相应的DFT并进行适当组合,达到删除重复计算,减少乘法运算和简化结构的目的。此后,在这思想基础上又开发了高基和分裂基等快速算法,随着数字技术的高速发展,1976年出现建立在数论和多项式理论基础上的维诺格勒傅里叶变换算法(WFTA)和素因子傅里叶变换算法。它们的共同特点是,当N是素数时,可以将DFT算转化为求循环卷积,从而更进一步减少乘法次数,提高速度。

4.部分源码

...................................................

reg [15:0]cnts;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

cnts <= 16'd0;

i_real_dat <= 16'b1111110000000000;

i_imag_dat <= 16'b0000000000111111;

end

else begin

if(i_enable == 1'b1)

begin

cnts <= cnts+16'd1;

if(cnts>=16'd17 & cnts<=16'd512-16)

begin

i_real_dat <= ~i_real_dat;

if (cnts[2]==1'b1)

i_imag_dat <= ~i_imag_dat;

else

i_imag_dat <= i_imag_dat;

end

end

else begin

cnts <= 16'd0;

i_real_dat <= 16'b1111110000000000;

i_imag_dat <= 16'b0000001111111111;

end

end

end

...........................................................................

FFT_tops FFT_tops_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_before_fft(i_before_fft),

.i_last_fft (i_last_fft),

.i_enable (i_enable),

.i_real_dat (i_real_dat),

.i_imag_dat (i_imag_dat),

.o_start (o_start),

.o_ends (o_ends),

.o_enable (o_enable),

.o_real_ifft (o_real_ifft),

.o_imag_ifft (o_imag_ifft)

);

initial

begin

i_before_fft2=1'b0;

#53540

i_before_fft2=1'b1;

#40

i_before_fft2=1'b0;

end

IFFT_tops IFFT_tops_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_before_fft(o_start),

.i_last_fft (o_ends),

.i_enable (o_enable),

.i_real_dat (o_real_ifft[31-9:7]),

.i_imag_dat (o_imag_ifft[31-9:7]),

.o_start (o_start2),

.o_ends (o_ends2),

.o_enable (o_enable2),

.o_real_ifft (o_real_ifft2),

.o_imag_ifft (o_imag_ifft2)

);

initial

begin

i_clk = 1'b1;

i_rst = 1'b1;

#10000

i_rst = 1'b0;

end

always #10 i_clk=~i_clk;

endmodule

A794