1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJWZlpdw

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

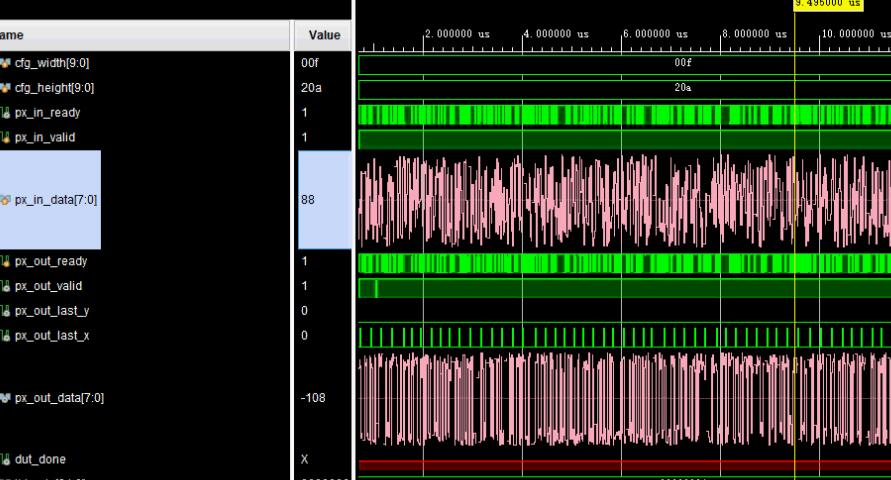

2.部分仿真图预览

3.算法概述

FIR(Finite Impulse Response)滤波器:有限长单位冲激响应滤波器,又称为非递归型滤波器,是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应是有限长的,因而滤波器是稳定的系统。因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。

4.部分源码

module xfilter(clk, rst,

i_valid_new_pixel,

i_new_pixel,

i_valid_lpos,

i_valid_cpos,

i_valid_rpos,

i_rowM,

o_valid_filt,

o_filt_pixel,

o_colN,

o_rowM

);

parameter XB = 10;

parameter PB = 8;

input clk;

input rst;

input i_valid_new_pixel;

input [(PB + 2) - 1:0] i_new_pixel;

input i_valid_lpos;

input i_valid_cpos;

input i_valid_rpos;

input i_rowM;

output o_valid_filt;

output [PB - 1:0] o_filt_pixel;

output o_colN;

output o_rowM;

reg [(PB + 4) - 1:0] r_pixel_sum = 0;

reg [PB - 1:0] rr_pixel_sum = 0;

reg r_valid_lpos = 0;

reg r_valid_cpos = 0;

reg r_valid_rpos = 0;

reg r_valid_filt_pixel = 0;

reg rr_valid_cpos = 0;

reg r_valid_pixel_in = 0;

reg rr_valid_pixel_in = 0;

........................................................................

always @(posedge clk)

begin

//read in pixel

r_valid_lpos <= i_valid_lpos;

r_valid_cpos <= i_valid_cpos;

r_valid_rpos <= i_valid_rpos;

rr_valid_cpos <= r_valid_cpos;

r_colN <= i_valid_rpos;

rr_colN <= r_colN;

rrr_colN <= rr_colN;

r_rowM <= i_rowM;

rr_rowM <= r_rowM;

rrr_rowM <= rr_rowM;

if (rst)

begin

r_valid_pixel_in <= 0;

rr_valid_pixel_in <= 0;

r_valid_filt_pixel <= 0;

end

else

begin

r_valid_pixel_in <= c_valid_pixel_in;

rr_valid_pixel_in <= r_valid_pixel_in;

r_valid_filt_pixel <= rr_valid_pixel_in;

end

r_pixel2 <= c_pixel2;

end

wire [PB + 4 - 1: 0] c_pixel_sum = (rr_valid_cpos) ? r_pixel_sum + r_pixel2 + 8: r_pixel_sum + 8;

reg r_valid_new_pixel = 0; //needed to check if new row's data was added

//add filter

always @(posedge clk)

begin

r_valid_new_pixel <= i_valid_new_pixel;

if (r_valid_rpos)

begin

if (r_valid_new_pixel) //new data added to queue

r_pixel_sum <= {c_pixel1, 1'd0} + c_pixel2;

else

r_pixel_sum <= {c_pixel0, 1'd0} + c_pixel1;

end

else

begin

r_pixel_sum <= c_pixel0 + {c_pixel1, 1'd0};

end

rr_pixel_sum <= c_pixel_sum[PB + 4 -1: 4];

end

//3 pixel buffer

queue PIXBUF (.clk(clk),

.i_valid_pixel(i_valid_new_pixel),

.i_pixel(i_new_pixel),

.o_pixel0(c_pixel0),

.o_pixel1(c_pixel1),

.o_pixel2(c_pixel2)

);

endmodule

module queue(clk, i_valid_pixel, i_pixel, o_pixel0, o_pixel1, o_pixel2);

parameter PB = 8;

.....................................................

endmodule

A411