1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJuTlJZu

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

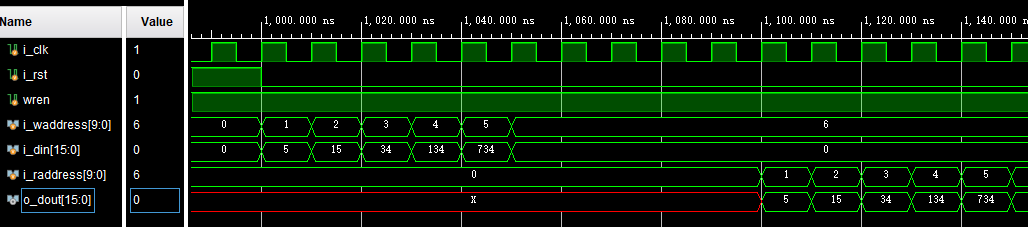

2.部分仿真图预览

3.算法概述

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,具有可重构性、高速度、低功耗等特点,被广泛应用于数字电路设计、信号处理、图像处理等领域。在FPGA中,实现各类存储器是非常重要的任务之一。存储器是计算机系统中的重要组成部分,用于存储程序和数据。在FPGA中,存储器包括RAM(Random Access Memory)、SRAM(Static Random Access Memory)等。本文将从专业角度详细介绍基于FPGA的各类存储器的实现步骤和数学原理。

4.部分源码

.....................................................................

module TEST_tops_sram();

reg [7:0] dataIn;

reg [7:0] Addr;

reg CS;

reg WE;

reg RD;

reg Clk;

// Outputs

wire [7:0] dataOut;

// Instantiate the Unit Under Test (UUT)

tops_sram uut (

.dataIn(dataIn),

.dataOut(dataOut),

.Addr(Addr),

.CS(CS),

.WE(WE),

.RD(RD),

.Clk(Clk)

);

initial begin

// Initialize Inputs

dataIn = 8'h0;

Addr = 8'h0;

CS = 1'b0;

WE = 1'b0;

RD = 1'b0;

Clk = 1'b0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

dataIn = 8'h0;

Addr = 8'h0;

CS = 1'b1;

WE = 1'b1;

RD = 1'b0;

#20;

dataIn = 8'h0;

Addr = 8'h0;

#20;

dataIn = 8'h1;

Addr = 8'h1;

#20;

dataIn = 8'h10;

Addr = 8'h2;

#20;

dataIn = 8'h6;

Addr = 8'h3;

#20;

dataIn = 8'h12;

Addr = 8'h4;

#40;

Addr = 8'h0;

WE = 1'b0;

RD = 1'b1;

#20;

Addr = 8'h1;

#20;

Addr = 8'h2;

#20;

Addr = 8'h3;

#20;

Addr = 8'h4;

end

always #10 Clk = ~Clk;

endmodule

00_025m