1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJWXk55w

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

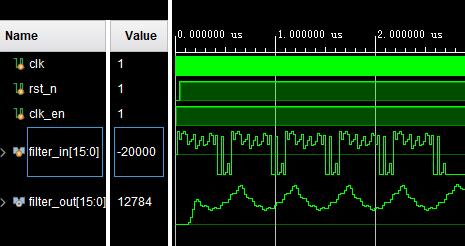

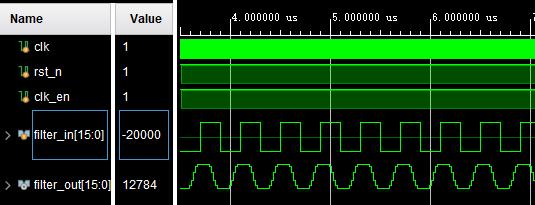

2.部分仿真图预览

3.算法概述

FIR(Finite Impulse Response)滤波器:有限长单位冲激响应滤波器,又称为非递归型滤波器,是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应是有限长的,因而滤波器是稳定的系统。因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。

在进入FIR滤波器前,首先要将信号通过A/D器件进行模数转换,把模拟信号转化为数字信号;为了使信号处理能够不发生失真,信号的采样速度必须满足香农采样定理,一般取信号频率上限的4-5倍做为采样频率;一般可用速度较高的逐次逼进式A/D转换器,不论采用乘累加方法还是分布式算法设计FIR滤波器,滤波器输出的数据都是一串序列,要使它能直观地反应出来,还需经过数模转换,因此由FPGA构成的FIR滤波器的输出须外接D/A模块。FPGA有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好,利用FPGA乘累加的快速算法,可以设计出高速的FIR数字滤波器。

4.部分源码

..........................................................

reg [15:0] delay_pipeline [0:8];

reg [23:0] product [0:8];

reg [26:0] sum;

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

delay_pipeline[0] <= 0;

delay_pipeline[1] <= 0;

delay_pipeline[2] <= 0;

delay_pipeline[3] <= 0;

delay_pipeline[4] <= 0;

delay_pipeline[5] <= 0;

delay_pipeline[6] <= 0;

delay_pipeline[7] <= 0;

delay_pipeline[8] <= 0;

end

else if(clk_en) begin

delay_pipeline[0] <= filter_in;

delay_pipeline[1] <= delay_pipeline[0];

delay_pipeline[2] <= delay_pipeline[1];

delay_pipeline[3] <= delay_pipeline[2];

delay_pipeline[4] <= delay_pipeline[3];

delay_pipeline[5] <= delay_pipeline[4];

delay_pipeline[6] <= delay_pipeline[5];

delay_pipeline[7] <= delay_pipeline[6];

delay_pipeline[8] <= delay_pipeline[7];

end

end

..............................................................

A383