1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJaXmZpw

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

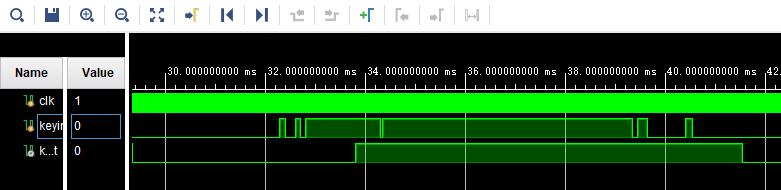

2.部分仿真图预览

3.算法概述

按键抖动的时间长短有机械按键的机械特性决定,分为前抖动和后抖动,一般为5ms~10ms。按键稳定闭合时间的长短由操作者的按键动作决定,一般为零点几秒至数秒。按键消抖原理就是在按键稳定时读取按键的状态,将该值作为FPGA是否触发的条件,并且要考虑后抖动(按键抬起)的影响,保证一次按键的按下操作只能触发一次FPGA。为确保按键对FPGA的触发可靠,本次实验将按键稳定闭合时间定为按键保持低电平单次持续20ms。当按键保持低电平单次持续为20ms时,即可认为按键按下操作有效,进而触发FPGA操作。

4.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

// Create Date: 2023/03/14 22:27:58

// Design Name:

// Module Name: tops_key

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tops_key(

input clk,

input keyin,

output reg keyout

);

.....................................................

parameter state0 = 3'b000;

parameter state1 = 3'b001;

parameter state2 = 3'b010;

parameter state3 = 3'b011;

parameter state4 = 3'b100;

reg [2:0] state = state0;

reg [16:0] timer = 17'b0;

reg timer_en = 1'b0, timer_tick = 1'b0;

always@ (posedge clk)

begin

case (state)

.......................................................

if (timer_en == 1'b1) begin

if (timer == (timerlim - 1)) begin

timer_tick <= 1'b1;

timer <= 17'b0;

end

else begin

timer_tick <= 1'b0;

timer <= timer + 17'b1;

end

end

else begin

timer <= 17'b0;

timer_tick <= 1'b0;

end

end

endmodule

A542