1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJ2Vkp5q

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

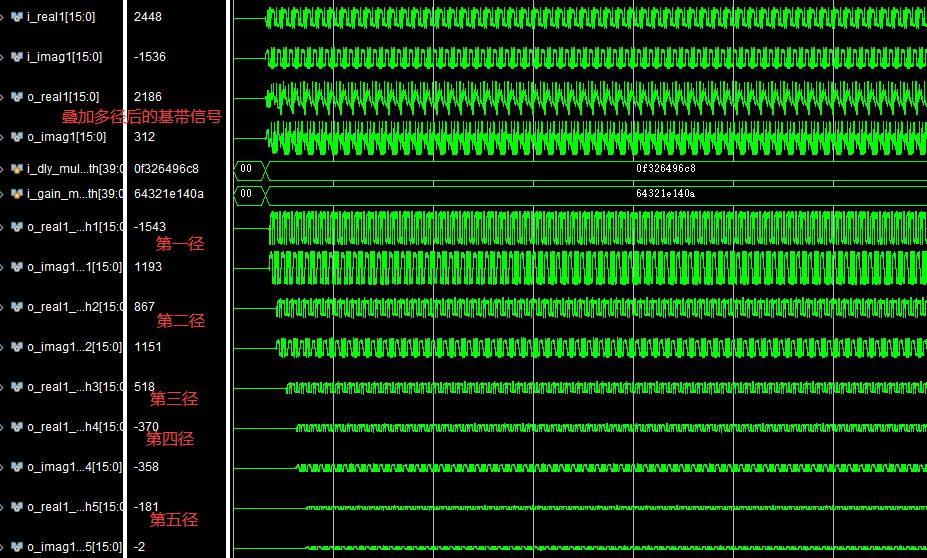

2.部分仿真图预览

3.算法概述

瑞利分布是一个均值为0,方差为σ2的平稳窄带高斯过程,其包络的一维分布是瑞利分布。其表达式及概率密度如图所示。瑞利分布是最常见的用于描述平坦衰落信号接收包络或独立多径分量接受包络统计时变特性的一种分布类型。两个正交高斯噪声信号之和的包络服从瑞利分布。

4.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/08/17 14:13:20

// Design Name:

// Module Name: TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST();

reg i_clk;

reg i_rst;

reg signed[7:0]i_SNR;//根据质量得到当前帧类型:-10~50

reg signed[15:0]i_fre;

wire signed[15:0]i_real1;

wire signed[15:0]i_imag1;

wire signed[15:0]o_Rnoise1;

wire signed[15:0]o_Inoise1;

wire signed[15:0]o_real1;

wire signed[15:0]o_imag1;

reg signed[1:0]i_Idiff;

reg signed[1:0]i_Qdiff;

initial

begin

i_Idiff = 2'b00;

#1440

repeat(12500)

begin

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b01;

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b11;

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b11;

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b11;

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b01;

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b01;

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b11;

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b01;

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b11;

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b01;

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b01;

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b01;

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b01;

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b11;

#10 i_Idiff = 2'b00;

#30 i_Idiff = 2'b11;

end

$stop();

end

initial

begin

i_Qdiff = 2'b00;

#1440

repeat(12500)

begin

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b11;

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b11;

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b01;

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b01;

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b01;

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b01;

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b11;

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b11;

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b11;

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b01;

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b11;

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b01;

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b11;

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b01;

#10 i_Qdiff = 2'b00;

#30 i_Qdiff = 2'b11;

end

$stop();

end

//测试信号源

wire signed[1:0] w_Inz=i_Idiff;

wire signed[1:0] w_Qnz=i_Qdiff;

//成型滤波

fiter uut1(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (w_Inz),

.o_dout (i_real1)

);

fiter uut2(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (w_Qnz),

.o_dout (i_imag1)

);

initial

begin

i_clk = 1'b1;

i_rst = 1'b1;

i_fre= 0;

i_SNR = 8'd0;

#1600

i_rst = 1'b0;

i_SNR = 25;

i_fre= 0;//1/2^15*100e6=3k频偏

end

always #5 i_clk=~i_clk;

reg signed[39:0]i_dly_multipath;//多径延迟,最大设置5个,每8位表示一个

reg signed[39:0]i_gain_multipath;//多径增益,最大设置5个,每8位表示一个

wire signed[15:0]o_real1_multipath1;

wire signed[15:0]o_imag1_multipath1;

wire signed[15:0]o_real1_multipath2;

wire signed[15:0]o_imag1_multipath2;

wire signed[15:0]o_real1_multipath3;

wire signed[15:0]o_imag1_multipath3;

wire signed[15:0]o_real1_multipath4;

wire signed[15:0]o_imag1_multipath4;

wire signed[15:0]o_real1_multipath5;

wire signed[15:0]o_imag1_multipath5;

initial

begin

i_dly_multipath=40'd0;

i_gain_multipath=40'd0;

#1600

//设置5个多径的延迟和增益

i_dly_multipath = {8'd15,8'd50,8'd100,8'd150,8'd200};

i_gain_multipath = {8'd100,8'd50,8'd30,8'd20,8'd10};

end

AWGN_tops AWGN_tops_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_SNR (i_SNR),//根据质量得到当前帧类型:-10~50

.i_fre (i_fre),

.i_dly_multipath(i_dly_multipath),

.i_gain_multipath(i_gain_multipath),

.i_real1 (i_real1),

.i_imag1 (i_imag1),

.o_Rnoise1 (o_Rnoise1),

.o_Inoise1 (o_Inoise1),

.o_real1 (o_real1),

.o_imag1 (o_imag1),

.o_real1_multipath1(o_real1_multipath1),

.o_imag1_multipath1(o_imag1_multipath1),

.o_real1_multipath2(o_real1_multipath2),

.o_imag1_multipath2(o_imag1_multipath2),

.o_real1_multipath3(o_real1_multipath3),

.o_imag1_multipath3(o_imag1_multipath3),

.o_real1_multipath4(o_real1_multipath4),

.o_imag1_multipath4(o_imag1_multipath4),

.o_real1_multipath5(o_real1_multipath5),

.o_imag1_multipath5(o_imag1_multipath5)

);

endmodule

00_038m

---