1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZpeXm5xs

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

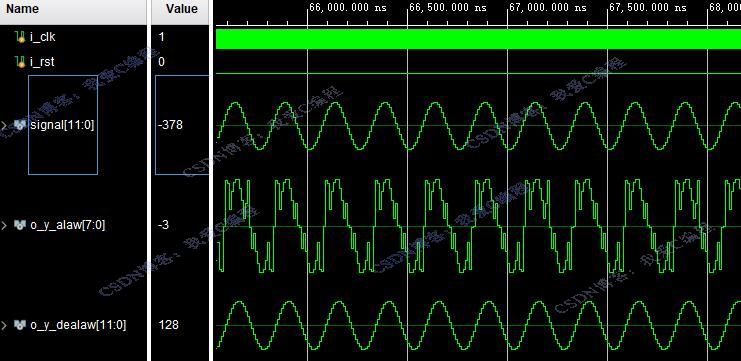

2.部分仿真图预览

3.算法概述

A律压缩是一种广泛应用于语音编码的非均匀量化技术,尤其在G.711标准中被欧洲和中国等国家采纳。该技术的核心目的是在有限的带宽下高效传输语音信号,同时保持较高的语音质量。在基于现场可编程门阵列(Field-Programmable Gate Array, FPGA)的实现中,A律压缩解压缩算法的高效硬件实现成为可能,这对于实时通信系统尤为重要。

4.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/06/21 17:39:11

// Design Name:

// Module Name: TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST();

reg i_clk;

reg i_rst;

wire [7:0] o_y_alaw;

wire [11:0] o_y_dealaw;

wire [31 : 0] m_axis_data_tdata;

dds_compiler_0 dds_compiler_0U (

.aclk(i_clk), // input wire aclk

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata), // output wire [15 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata() // output wire [31 : 0] m_axis_phase_tdata

);

wire signed[11:0]signal = {m_axis_data_tdata[31],m_axis_data_tdata[31:21]};

tops uut(

.i_clk (i_clk),

.i_rst (i_rst),

.i_x (signal),

.o_y_alaw (o_y_alaw),

.o_y_dealaw (o_y_dealaw)

);

initial

begin

i_clk=1'b1;

i_rst=1'b1;

#100

i_rst=1'b0;

end

always #5 i_clk = ~i_clk;

endmodule

00_068m

---