1.完整项目描述和程序获取

>面包多安全交易平台:

vivado版本:https://mbd.pub/o/bread/ZJiYlZZs

quartusii版本:https://mbd.pub/o/bread/ZJiYlZZp

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

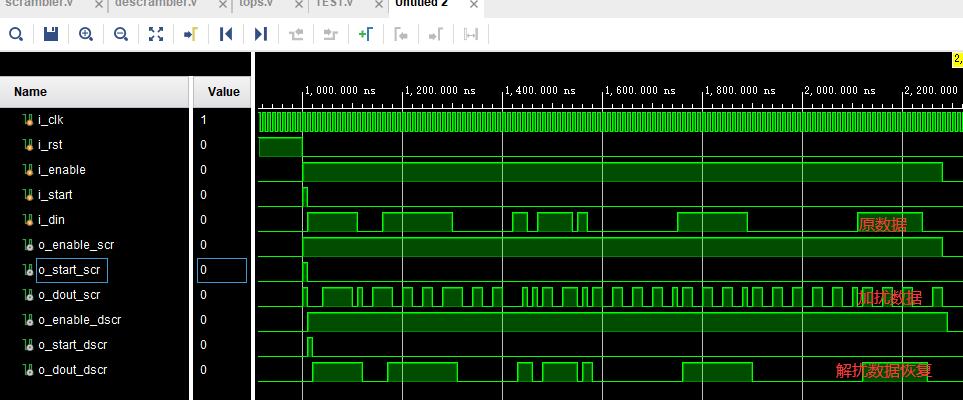

2.部分仿真图预览

3.算法概述

数据加扰是指在传输数据之前,对原始数据进行一定的变换,使得数据在传输时呈现出更加随机的特征。这样可以有效地抵御各种形式的干扰,包括电磁干扰、信道噪声、多径衰落等。数据加扰的基本原理是通过一定的算法,将原始数据进行一定的变换,使得变换后的数据在统计特性上与原始数据不同。这样可以使得传输过程中的干扰和噪声对数据的影响降低,从而提高数据传输的可靠性。

4.部分源码

`timescale 1ns / 1ps

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST();

reg i_clk;

reg i_rst;

reg i_enable;

reg i_start;

reg i_din;

wire o_enable_scr;

wire o_start_scr;

wire o_dout_scr;

wire o_enable_dscr;

wire o_start_dscr;

wire o_dout_dscr;

tops uut(

.i_clk (i_clk),

.i_rst (i_rst),

.i_enable (i_enable),

.i_start (i_start),

.i_din (i_din),

.o_enable_scr (o_enable_scr),

.o_start_scr (o_start_scr),

.o_dout_scr (o_dout_scr),

.o_enable_dscr (o_enable_dscr),

.o_start_dscr (o_start_dscr),

.o_dout_dscr (o_dout_dscr)

);

initial

begin

i_clk = 1'b1;

i_rst = 1'b1;

#1000

i_rst = 1'b0;

end

initial

begin

i_enable = 1'b0;

#1000

i_enable = 1'b1;

#1280

i_enable = 1'b0;

end

initial

begin

i_start = 1'b0;

#1000

i_start = 1'b1;

#10

i_start = 1'b0;

end

initial

begin

i_din = 1'b0;

#1000

i_din = 1'b0;

#10

i_din = 1'b1;

#100

i_din = 1'b0;

#50

i_din = 1'b1;

#140

i_din = 1'b0;

#120

i_din = 1'b1;

#30

i_din = 1'b0;

#20

i_din = 1'b1;

#70

i_din = 1'b0;

#10

i_din = 1'b1;

#20

i_din = 1'b0;

#130

i_din = 1'b0;

#50

i_din = 1'b1;

#140

i_din = 1'b0;

#220

i_din = 1'b1;

#130

i_din = 1'b0;

#1000

$stop();

end

always #5 i_clk=~i_clk;

endmodule

00_006m