1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/Y5qVk5ty

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

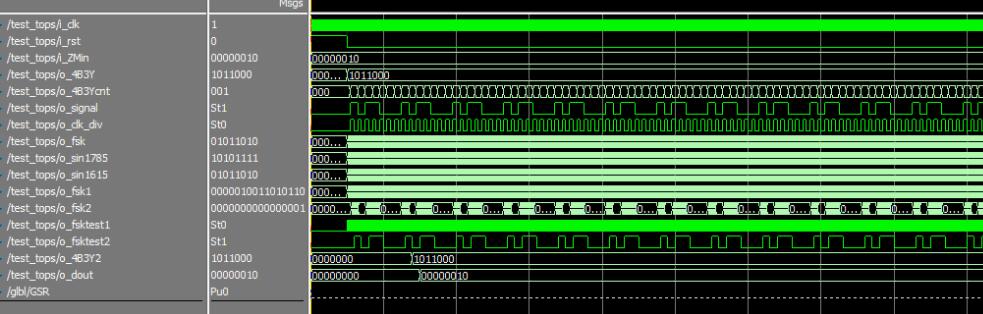

2.部分仿真图预览

3.算法概述

窄带直接印字电报 NBDP (Narrow Band Direct Pringting Telegraph)是国际海事组织IMO(International Maritime Organization)的无线通信技术之一,适用为中高频段MF/HF。中高频NBDP系统是船与岸,船与船之间的海上无线电通信有效终端之一。NBDP系统由船舶电台、海岸电台,ARQ单元模块组成。ARQ单元是单边带收发信机之间的主体设备。

本研究根据软件无线电的思想,设计NDBP系统的基带2FSK调制解调模块,信源编码译码模块,信道模块,重发模块和反馈控制模块,为工程实践提供有效ARQ解决方案。通过本项目锻炼学生综合应用通信专业工程基础理论解决复杂工程问题实践能力。

4.部分源码

module tops(

i_clk,

i_rst,

i_ZMin,

//signal

o_4B3Y,

o_4B3Ycnt,

o_signal,

o_clk_div,

//FSK mode

o_fsk,

o_sin1785,

o_sin1615,

//FSK Demode

o_fsk1,

o_fsk2,

o_fsktest1,

o_fsktest2,

o_4B3Y2,

o_dout

);

input i_clk;

input i_rst;

input [7:0]i_ZMin;

output [6:0]o_4B3Y;

output [2:0]o_4B3Ycnt;

output o_signal;

output o_clk_div;

output signed[7:0]o_fsk;

output signed[7:0]o_sin1785;

output signed[7:0]o_sin1615;

output signed[15:0]o_fsk1;

output signed[15:0]o_fsk2;

output o_fsktest1;

output o_fsktest2;

output[6:0]o_4B3Y2;

output[7:0]o_dout;

//code,7 element constant ratio code

S7ele_ratio_code S7ele_ratio_code_u (

.i_clk (i_clk),

.i_rst (i_rst),

.i_ZMin (i_ZMin),

.o_4B3Y (o_4B3Y),

.o_4B3Ycnt(o_4B3Ycnt),

.o_signal (o_signal),

.o_clk_div(o_clk_div)

);

//fsk mod

fsk_mod fsk_mod_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (o_signal),

.o_fsk (o_fsk),

.o_sin1785(o_sin1785),

.o_sin1615(o_sin1615)

);

//fsk demode

fsk_demod fsk_demod_u(

.i_clk (i_clk),

.i_clk2 (~o_clk_div),

.i_rst (i_rst),

.i_fsk (o_fsk),

.o_fsk (o_fsk1),

.o_fsk2 (o_fsk2),

.o_fsktest1(o_fsktest1),

.o_fsktest2(o_fsktest2)

);

//decode

S7ele_ratio_decode S7ele_ratio_decode_u(

.i_clk (~o_clk_div),

.i_rst (i_rst),

.i_din (o_fsktest2),

.o_4B3Y(o_4B3Y2),

.o_dout(o_dout)

);

endmodule

01-156m