1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/Z56bm55x

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

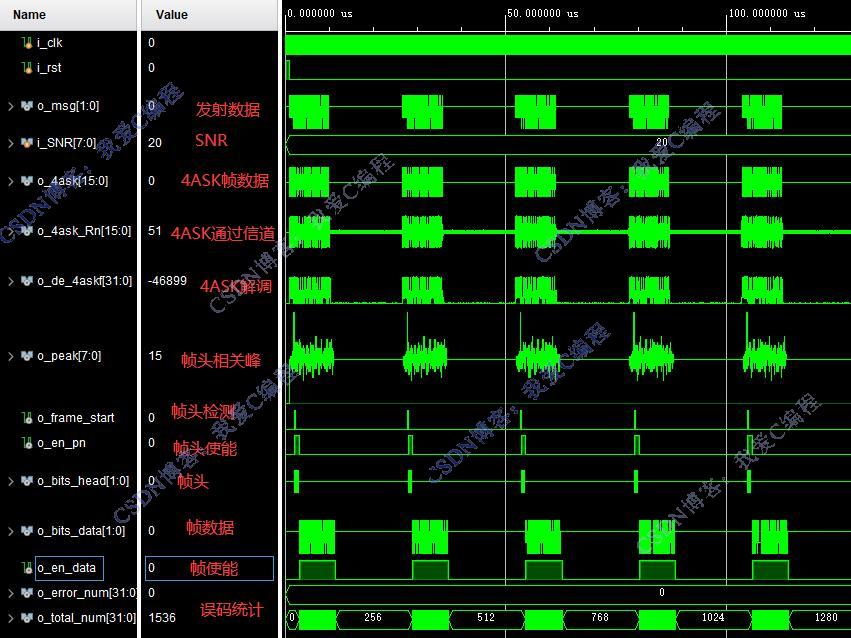

2.部分仿真图预览

3.算法概述

在现代通信系统中,数字调制技术被广泛应用于无线通信、卫星通信以及有线通信等领域。其中,振幅键控(Amplitude Shift Keying, ASK)是一种简单的数字调制方式,通过改变载波信号的幅度来表示不同的数据位。四进制振幅键控(4-ASK)是ASK的一种扩展形式,它使用四个不同的幅度等级来传输两个比特的信息。

4.部分源码

.......................................................................

//调制

ASK4_mod ASK4_mod_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_bits (i_bits),

.o_4ask (o_4ask)

);

awgns awgns_u(

.i_clk(i_clk),

.i_rst(i_rst),

.i_SNR(i_SNR), //这个地方可以设置信噪比,数值大小从-10~50,

.i_din(o_4ask),

.o_noise(),

.o_dout(o_4ask_Rn)

);

解调//解调//解调//解调//解调//解调//解调//解调//解调//解调//解调//解调//解调

ASK4_demod ASK4_demod_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_4ask (o_4ask_Rn),

.o_de_4ask (o_de_4ask),

.o_de_4askf (o_de_4askf),

.o_bits (o_bits),

.o_bits_data (o_bits_data),

.o_bits_head (o_bits_head),

.o_peak (o_peak),

.o_en_data (o_en_data),

.o_en_pn (o_en_pn),

.o_frame_start (o_frame_start)

);

//error calculate

Error_Chech Error_Chech_u(

.i_clk(i_clk),

.i_rst(i_rst),

.i_trans(i_bits),

.i_en_data(o_en_data),

.i_rec(o_bits),

.o_error_num(o_error_num),

.o_total_num(o_total_num),

.o_rec2()

);

endmodule

0sj2_061m

---