1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZZ2Ykp5p

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

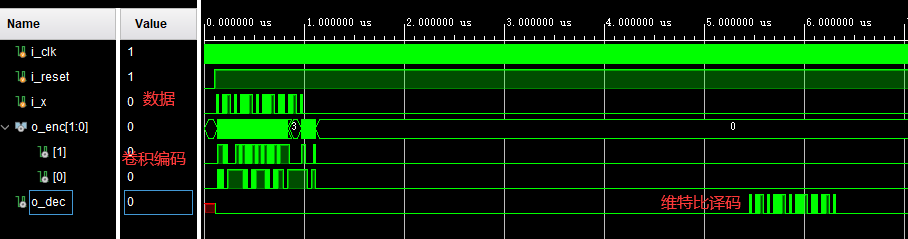

2.部分仿真图预览

3.算法概述

维特比译码是用于最大似然序列估计的一种动态规划算法,广泛应用于卷积编码以及其他序列编码的译码过程中。在卷积编码中,维特比译码器通过构造一棵称为“状态转移图”或“trellis”的树状结构来寻找最有可能的原始信息序列路径。

4.部分源码

`timescale 1ns / 1ps

// Company:

// Engineer:

//

module TEST;

// Inputs

reg i_clk;

reg i_reset;

reg i_x;

// Outputs

wire [1:0] o_enc;

wire o_dec;

// Instantiate the Unit Under Test (UUT)

conv_217_code uut (

.i_clk (i_clk),

.i_reset (~i_reset),

.i_x (i_x),

.o_enc (o_enc)

);

conv_217_decode uut2 (

.i_clk (i_clk),

.i_reset (~i_reset),

.i_enc (o_enc),

.o_dec (o_dec)

);

always #10 i_clk = ~i_clk;

initial begin

// Initialize Inputs

i_clk = 0;

i_reset = 0;

i_x = 0;

// Wait 100 ns for global i_reset to finish

#100;

i_reset = 1;

// Add stimulus here

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 1;

#20

i_x = 0;

#20

i_x = 0;

#20

i_x = 1;

#20

i_x = 0;

end

endmodule

00_060m

---