1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJebmZxv

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

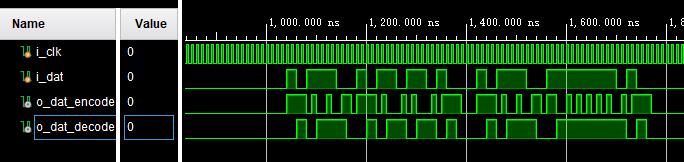

2.部分仿真图预览

3.算法概述

viterbi译码算法是一种卷积码的解码算法。优点不说了。缺点就是随着约束长度的增加算法的复杂度增加很快。约束长度N为7时要比较的路径就有64条,为8时路径变为128条。 (2<<(N-1))。所以viterbi译码一般应用在约束长度小于10的场合中。

先说编码(举例约束长度为7):编码器7个延迟器的状态(0,1)组成了整个编码器的64个状态。每个状态在编码器输入0或1时,会跳转到另一个之中。比如110100输入1时,变成101001(其实就是移位寄存器)。并且输出也是随之而改变的。

这样解码的过程就是逆过程。算法规定t时刻收到的数据都要进行64次比较,就是64个状态每条路有两条分支(因为输入0或1),同时,跳传到不同的两个状态中去,将两条相应的输出和实际接收到的输出比较,量度值大的抛弃(也就是比较结果相差大的),留下来的就叫做幸存路径,将幸存路径加上上一时刻幸存路径的量度然后保存,这样64条幸存路径就增加了一步。在译码结束的时候,从64条幸存路径中选出一条量度最小的,反推出这条幸存路径(叫做回溯),得出相应的译码输出。

4.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/04/16 22:37:19

// Design Name:

// Module Name: TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

module TEST();

reg i_clk;

reg i_dat;

wire o_dat_encode;

wire o_dat_decode;

tops tops_U(

.i_clk (i_clk),

.i_dat (i_dat),

.o_dat_encode (o_dat_encode),

.o_dat_decode (o_dat_decode)

);

initial

begin

i_clk=1'b1;

end

always #5 i_clk=~i_clk;

initial

begin

i_dat=1'b0;

#1020

{i_dat} =1'b0;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b1;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b0;

#20

{i_dat} =1'b0;

#200

$stop();

end

endmodule

A491