核心提示:01_115m,,含FPGA,matlab,文档及操作录像...

1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/Y5mUlZ5t

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

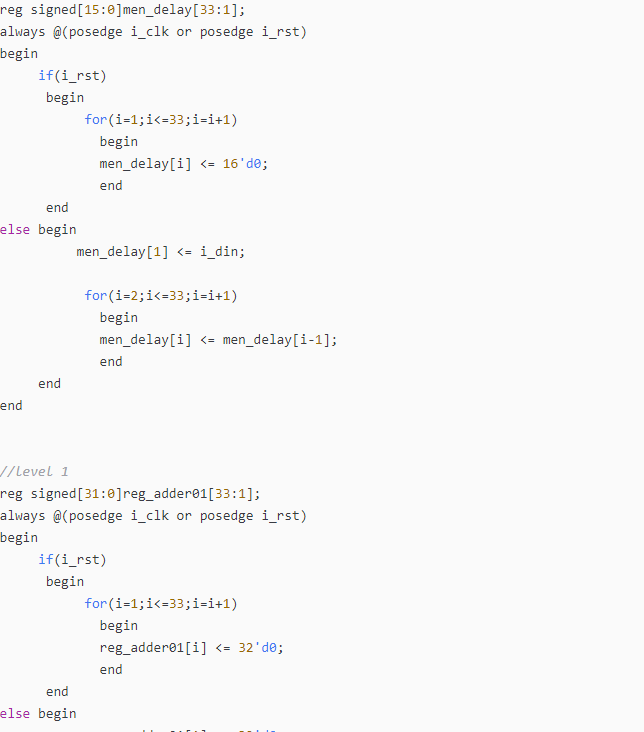

2.部分源码

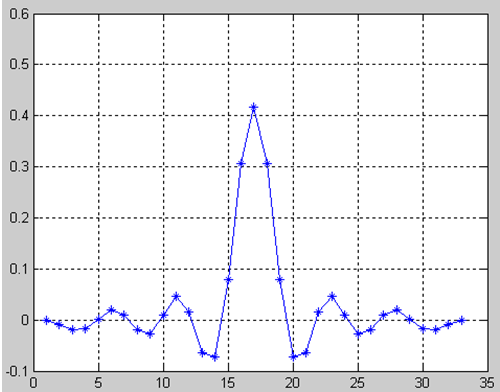

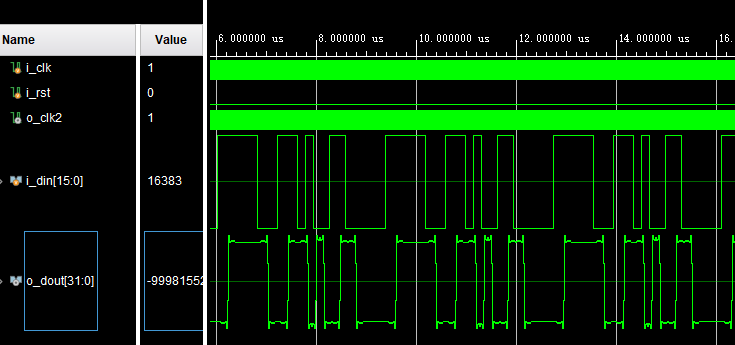

3.部分仿真图预览

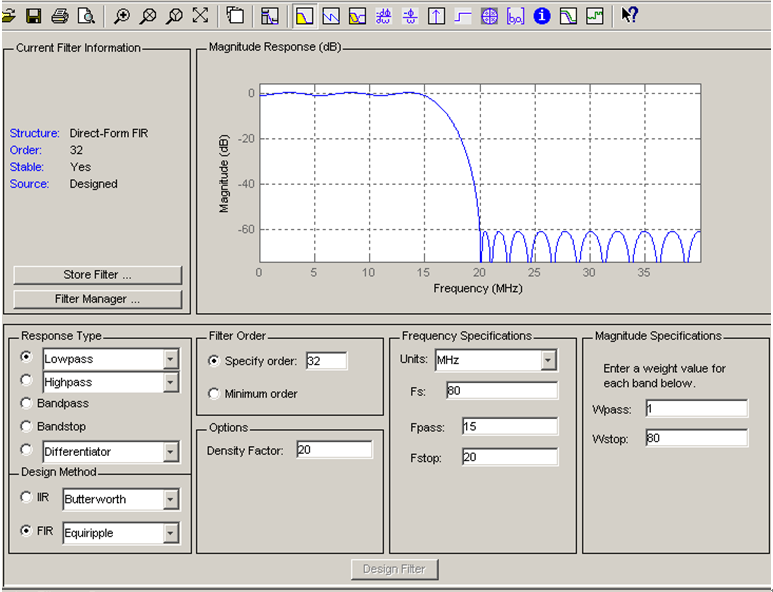

4.算法概述

HBF模块由半带滤波器(HBF)和抽取模块组成。该模块的任务是实现2倍抽取进一步降低信号采样速率。由于HBF的冲激响应h(k)除零点外其余偶数点均为零,所以用HBF实现2倍抽取可以节省一半的运算量,对增强软件无线电的实时性非常重要,HBF还具有参数约束少,设计容易、方便的特点。半带滤波器的主要作用是滤除信号高频部分,防止抽取过程后信号发生频谱混叠。在实际中,需要将输入信号进行多次滤波和抽取,并逐次降低采样率,同时也降低对每一级抗混叠滤波器的要求,所以需要使用半带滤波器进行设计与实现。

阻带衰减: ≥50dB

通带不平坦度:≤2dB

通常情况下,半带滤波器的有三种基本的结构,一般结构,转置结构以及复用结构,下面我们将针对这三种结构的滤波效果以及硬件占用情况进行分析,从而选用最佳的设计方案。