核心提示:01_115m,包含FPGA,matlab,设计文档以及操作录像...

1.完整项目描述和程序获取

>面包多安全交易平台

VIVADO版本:https://mbd.pub/o/bread/Y5mUlZlp

Quartusii版本:https://mbd.pub/o/bread/ZJiYlZpx

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

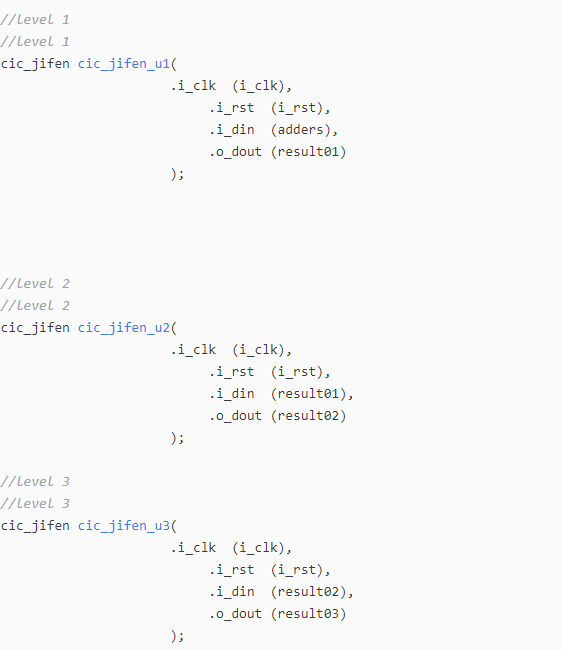

2.部分源码

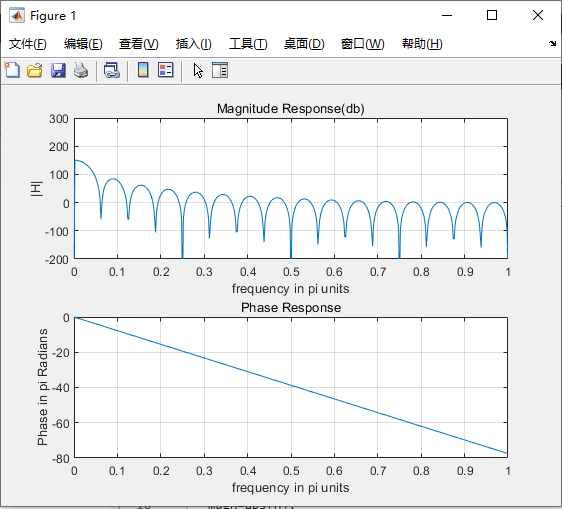

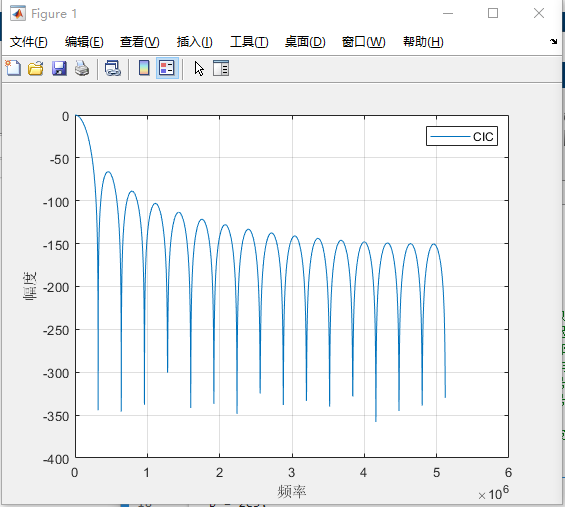

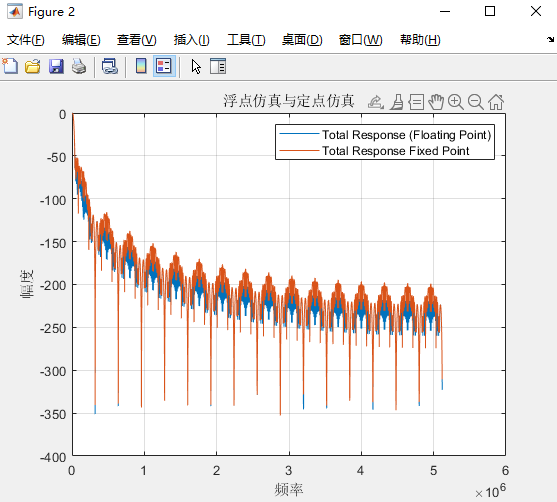

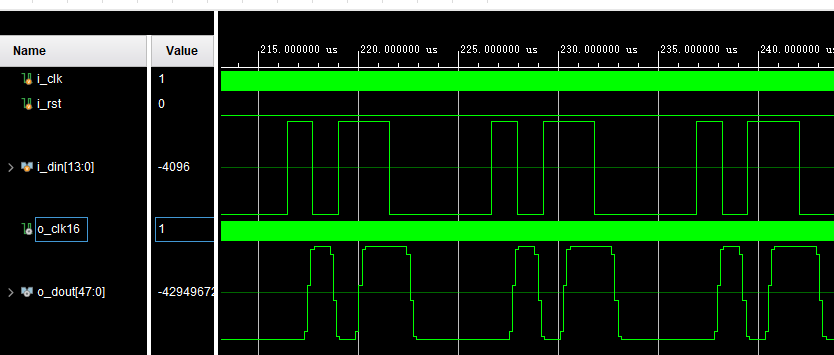

3.部分仿真图预览

4.算法概述

这里设计的五级CIC滤波器。那么其基本结构如上图所示,在降采样的左右都有五个延迟单元。

但是在CIC滤波的时候,会导致输出的位宽大大增加,但是如果单独对中间的处理信号进行截位,这会导致处理精度不够,从而影响整个系统的性能,所以,这里我们首先将输入的信号进行扩展。

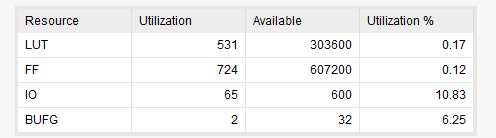

由于我们输入的中频信号通过ADC是位宽为14,在下变频之后,通过截位处理,其输出的数据仍为14位,所以,我们将CIC滤波的输入为14位,但是考虑到处理中间的益处情况以及保证处理精度的需要,我们首先将输入位宽扩展为40位,从而保证了处理精度以及溢出的情况。

这里首先说明一下为什么使用的级别是5级。从硬件资源角度考虑,CIC滤波器的级数太高,会导致最终输出的数据位宽很大,通过简单的验证,当CIC的级数大于5的时候,输出的位宽>50。这显然会导致硬件资源的大量占用,如果CIC级数太小,比如1,2级。这在其处理效果上没有任何意义,基本无法达到预计的效果,通过仿真分析,一般情况下,选择4级,5级比较合理,因此,这里我们选择5级的CIC滤波器。