1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJaZkp1u

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

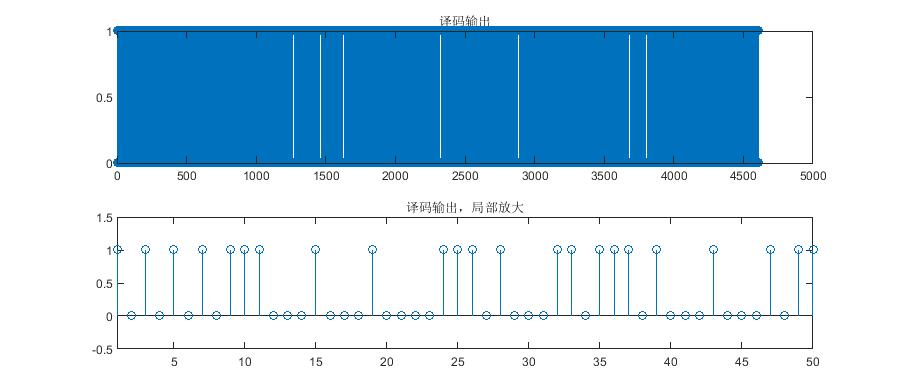

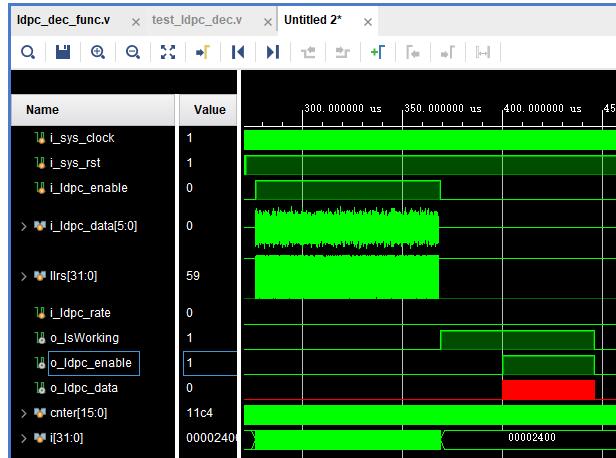

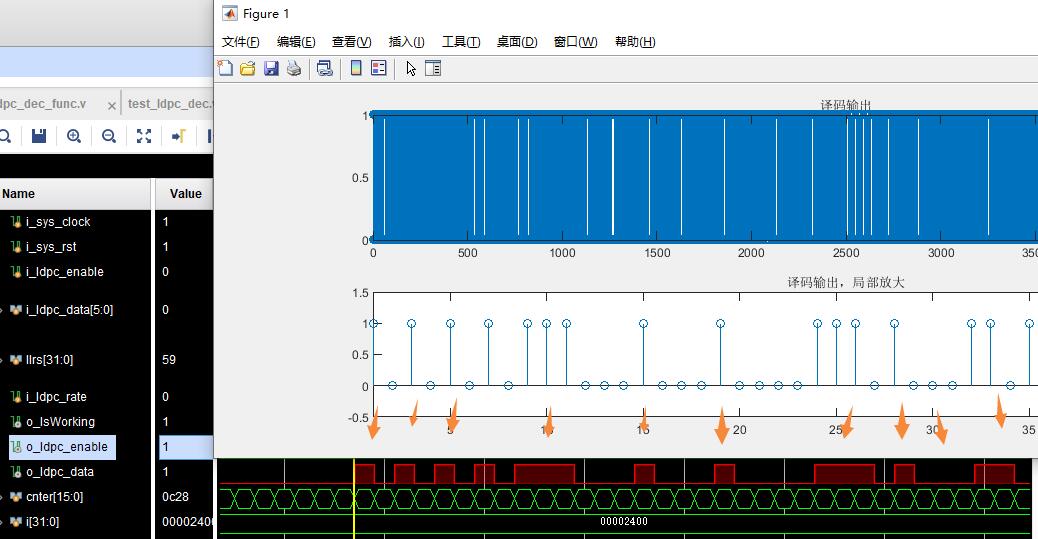

2.部分仿真图预览

3.算法概述

其中最小和算法的译码过程如下所示:

基于最小和算法的译码器设计的基本思想是:根据密度进化理论优化量化译码器参数,使量化译码器能达到最高的阈值。

整个算法的流程按如下步骤进行:

第一:初始化各个变量节点的值,赋初值;

第二:判断迭代次数是否已经超过了预设的最大迭代次数,如果超过,则迭代结束;

第三:每次迭代,变量节点的信息进行更新;

第四:计算每个变量节点Vn上的L值

第五:对每个变量节点Vn,对L值进行判决,输出序列Vk,从而结束译码;

最小和算法在本质上和BP译码算法相似,此外,整个算法采用对数域进行。

4.部分源码

............................................................................

reg[12:0]cnt;

reg[35:0]o_read_select;

reg o_read_enable;

reg[7:0] o_address;

reg[35:0]dout_tmp_r;

assign Max_lens = i_code_rate ? 13'd6911: 13'd4607;

assign finishs = (cnt == Max_lens);

always @(posedge i_sys_clk or negedge i_sys_rst)

begin

if(!i_sys_rst)

cnt <= 13'h0;

else if(i_state[3])

begin

if(finishs)

cnt <= 13'h0;

else

cnt <= cnt + 1'b1;

end

end

llr_values llr_values_u(

.i_clk (i_sys_clk),

.i_address(cnt),

.o_values (dout_tmp)

);

always @(posedge i_sys_clk or negedge i_sys_rst)

begin

if(!i_sys_rst)

o_address <= 8'd0;

else

o_address <= dout_tmp[13:6];

end

always @(posedge i_sys_clk or negedge i_sys_rst)

begin

if(!i_sys_rst)

o_read_select <= 36'd0;

else if(i_state[3])

o_read_select <= dout_tmp_r;

else

o_read_select <= 36'd0;

end

always @ (posedge i_sys_clk or negedge i_sys_rst)

begin

if(!i_sys_rst)

o_read_enable <= 1'b0;

else

o_read_enable <= i_state[3];

end

always @(dout_tmp[5:0])

case(dout_tmp[5:0])

6'd0 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0000_0000_0000_0001;

6'd1 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0000_0000_0000_0010;

6'd2 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0000_0000_0000_0100;

6'd3 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0000_0000_0000_1000;

6'd4 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0000_0000_0001_0000;

6'd5 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0000_0000_0010_0000;

6'd6 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0000_0000_0100_0000;

6'd7 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0000_0000_1000_0000;

6'd8 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0000_0001_0000_0000;

6'd9 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0000_0010_0000_0000;

6'd10 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0000_0100_0000_0000;

6'd11 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0000_1000_0000_0000;

6'd12 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0001_0000_0000_0000;

6'd13 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0010_0000_0000_0000;

6'd14 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_0100_0000_0000_0000;

6'd15 : dout_tmp_r = 36'b0000_0000_0000_0000_0000_1000_0000_0000_0000;

6'd16 : dout_tmp_r = 36'b0000_0000_0000_0000_0001_0000_0000_0000_0000;

6'd17 : dout_tmp_r = 36'b0000_0000_0000_0000_0010_0000_0000_0000_0000;

6'd18 : dout_tmp_r = 36'b0000_0000_0000_0000_0100_0000_0000_0000_0000;

6'd19 : dout_tmp_r = 36'b0000_0000_0000_0000_1000_0000_0000_0000_0000;

6'd20 : dout_tmp_r = 36'b0000_0000_0000_0001_0000_0000_0000_0000_0000;

6'd21 : dout_tmp_r = 36'b0000_0000_0000_0010_0000_0000_0000_0000_0000;

6'd22 : dout_tmp_r = 36'b0000_0000_0000_0100_0000_0000_0000_0000_0000;

6'd23 : dout_tmp_r = 36'b0000_0000_0000_1000_0000_0000_0000_0000_0000;

6'd24 : dout_tmp_r = 36'b0000_0000_0001_0000_0000_0000_0000_0000_0000;

6'd25 : dout_tmp_r = 36'b0000_0000_0010_0000_0000_0000_0000_0000_0000;

6'd26 : dout_tmp_r = 36'b0000_0000_0100_0000_0000_0000_0000_0000_0000;

6'd27 : dout_tmp_r = 36'b0000_0000_1000_0000_0000_0000_0000_0000_0000;

6'd28 : dout_tmp_r = 36'b0000_0001_0000_0000_0000_0000_0000_0000_0000;

6'd29 : dout_tmp_r = 36'b0000_0010_0000_0000_0000_0000_0000_0000_0000;

6'd30 : dout_tmp_r = 36'b0000_0100_0000_0000_0000_0000_0000_0000_0000;

6'd31 : dout_tmp_r = 36'b0000_1000_0000_0000_0000_0000_0000_0000_0000;

6'd32 : dout_tmp_r = 36'b0001_0000_0000_0000_0000_0000_0000_0000_0000;

6'd33 : dout_tmp_r = 36'b0010_0000_0000_0000_0000_0000_0000_0000_0000;

6'd34 : dout_tmp_r = 36'b0100_0000_0000_0000_0000_0000_0000_0000_0000;

6'd35 : dout_tmp_r = 36'b1000_0000_0000_0000_0000_0000_0000_0000_0000;

default:dout_tmp_r = 36'b0000_0000_0000_0000_0000_0000_0000_0000_0000;

endcase

endmodule

14_033_m