1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJaWmptp

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

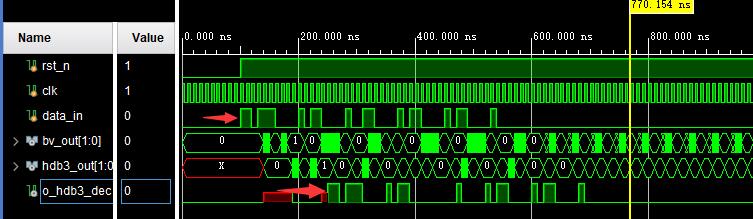

2.部分仿真图预览

3.算法概述

数字基带信号的传输是数字通信系统的重要组成部分。在数字通信中,有些场合可不经过载波调制和解调过程,而对基带信号进行直接传输。采用AMI码的信号交替反转,有可能出现四连零现象,这不利于接收端的定时信号提取。而HDB3码因其无直流成份、低频成份少和连0个数最多不超过三个等特点,而对定时信号的恢复十分有利,并已成为CCITT协会推荐使用的基带传输码型之一。

三阶高密度双极性码(英语:High Density Bipolar of Order 3 code,简称:HDB3码)是一种适用于基带传输的编码方式,它是为了克服AMI码的缺点而出现的,具有能量分散,抗破坏性强等特点。

三阶高密度双极性码用于所有层次的欧洲E-carrier系统,HDB3码将4个连续的“0”位元取代成“B00V”。这个做法可以确保连续的violations are of differing polarity,即是相隔单数的一般B记号。

1、连0的个数不超过3时,规则与AMI相同,即0不变,1变为-1、+1交替;

2、若连0的个数超过3,则将每4个0看作一小节,定义为B00V,B可以是-1、0、+1,V可以是-1、+1;

3、B和V具体值满足以下条件:V和前面相邻非0符号极性相同;不看V时极性交替;V与V之间极性交替;

4、一般第一个B取0,第一个非0符取-1。

4.部分源码

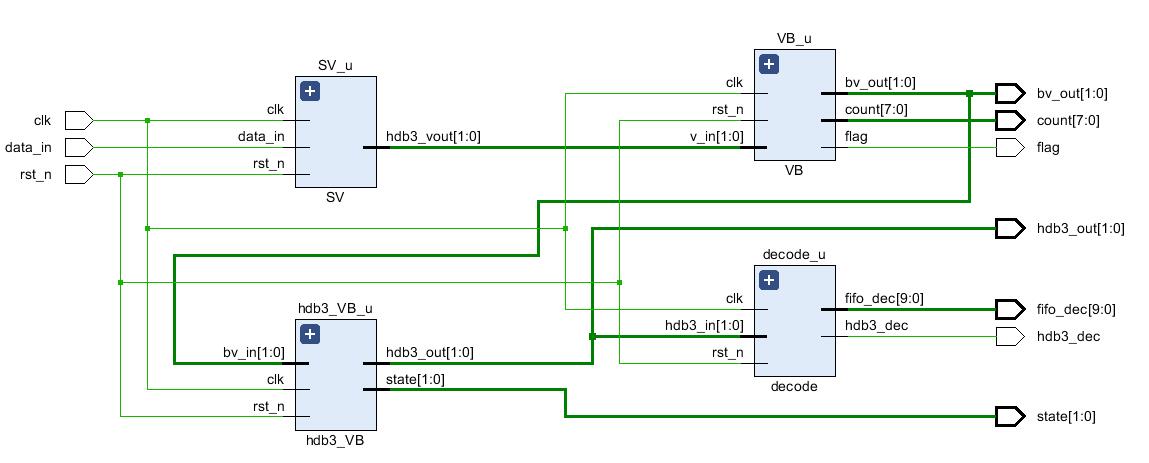

`timescale 1ns / 1ps

module hdb3(

input rst_n,clk,data_in,

output [1:0] bv_out,hdb3_out,state,

output flag,

output [7:0] count,

output hdb3_dec,

output [9:0] fifo_dec

);

wire [1:0] hdb3_vout;

wire [1:0] v_in;

wire [1:0] bv_in;

wire [1:0] hdb3_in;

VB VB_u(

.rst_n (rst_n),

.clk (clk),

.v_in (v_in),

.bv_out (bv_out),

.flag (flag),

.count (count)

);

SV SV_u(

.rst_n (rst_n),

.clk (clk),

.data_in (data_in),

.hdb3_vout (hdb3_vout)

);

hdb3_VB hdb3_VB_u(

.rst_n (rst_n),

.clk (clk),

.bv_in (bv_in),

.hdb3_out (hdb3_out),

.state (state)

);

decode decode_u(

.rst_n (rst_n),

.clk (clk),

.hdb3_in (hdb3_in),

.hdb3_dec (hdb3_dec),

.fifo_dec (fifo_dec)

);

assign v_in = hdb3_vout;

assign bv_in = bv_out;

assign hdb3_in = hdb3_out;

endmodule

A494