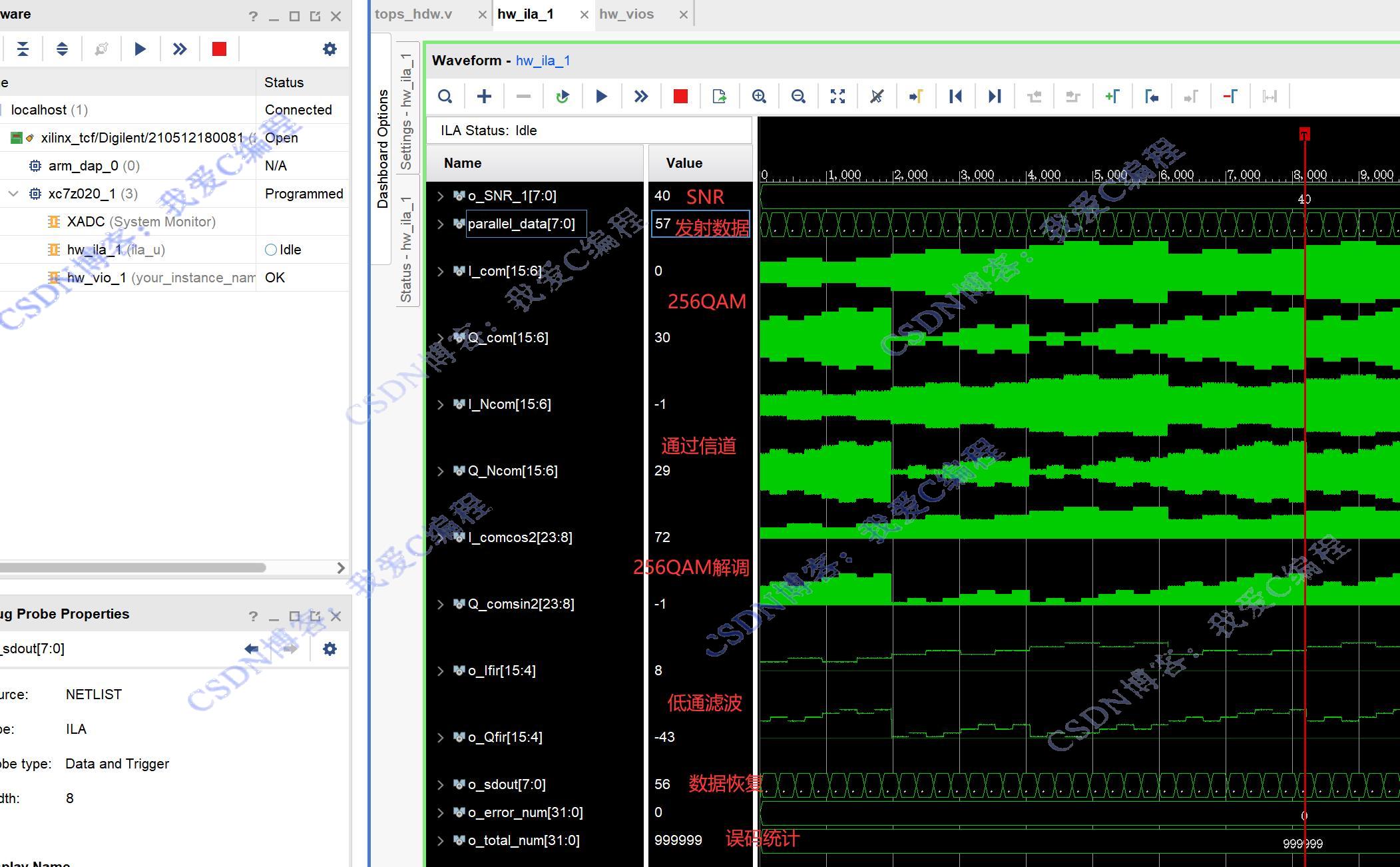

- 【硬件测试】基于FPGA的256QAM基带通信系统开发与硬件片内测试,包含信道模块,误码统计模块,可 2024-12-05 点击:21 评论:0

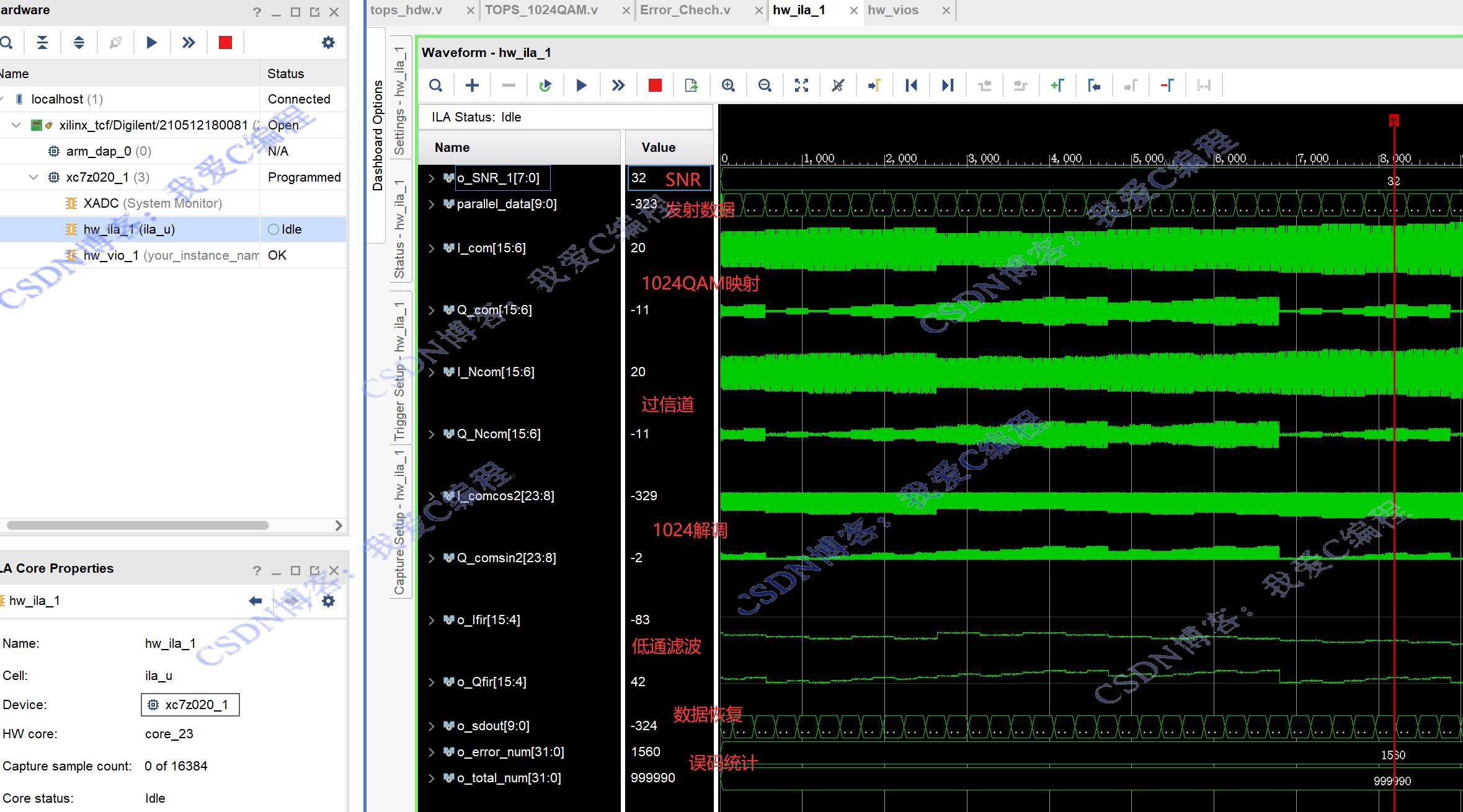

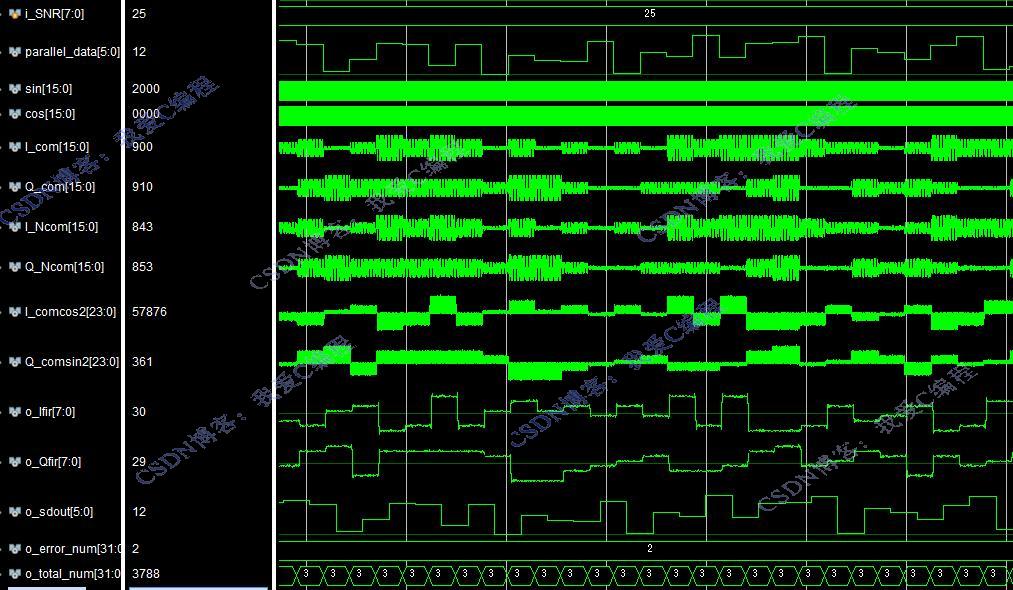

- 【硬件测试】基于FPGA的1024QAM基带通信系统开发与硬件片内测试,包含信道模块,误码统计模块, 2024-12-05 点击:17 评论:0

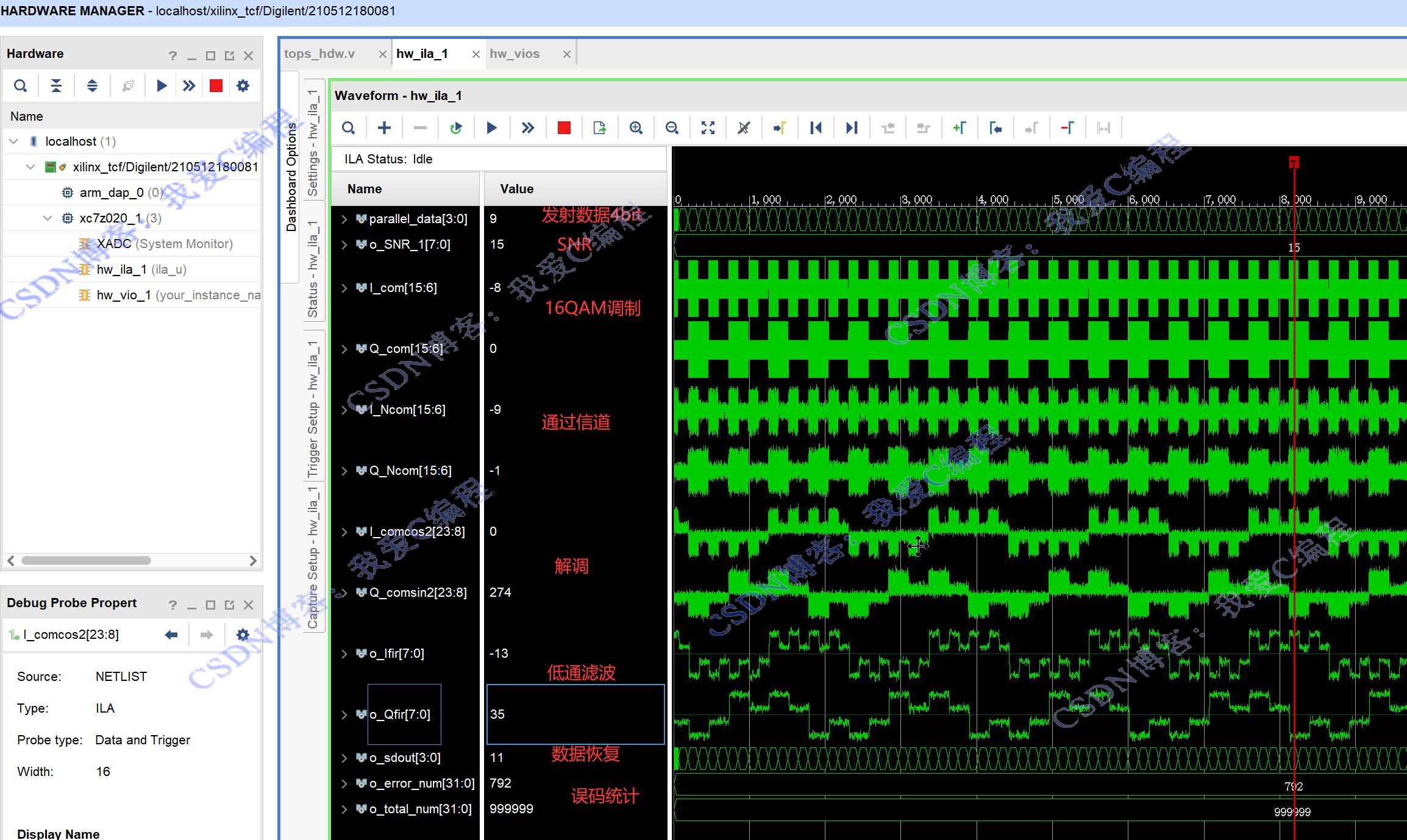

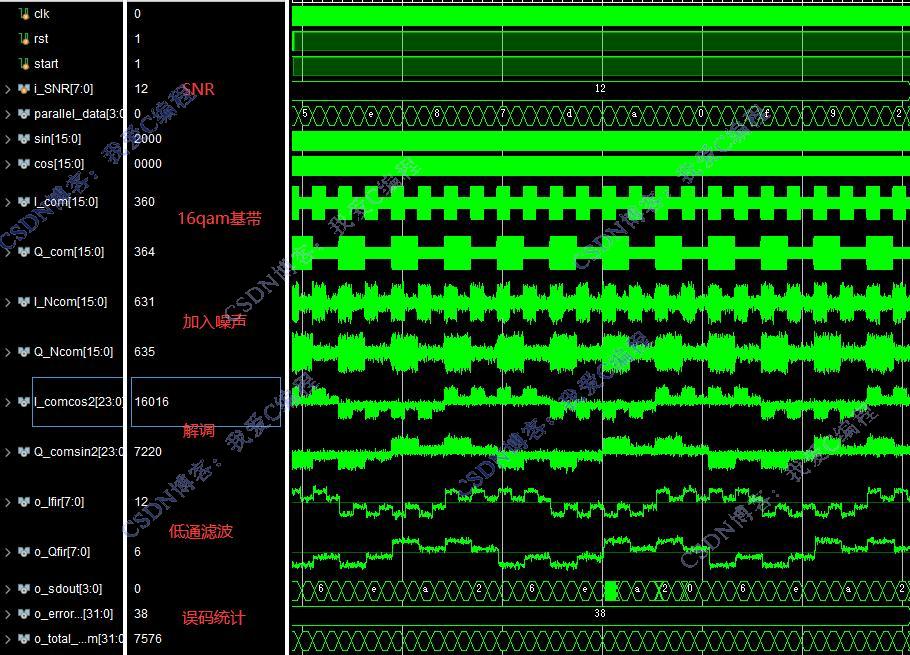

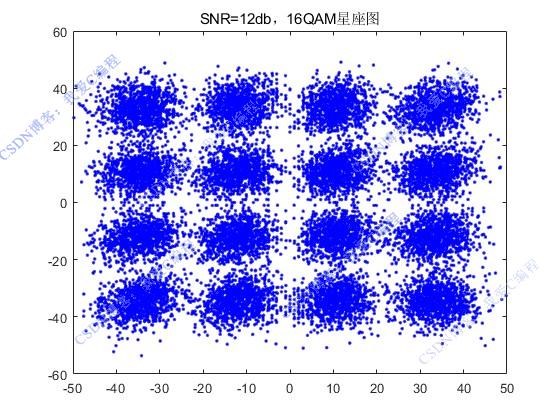

- 【硬件测试】基于FPGA的16QAM基带通信系统开发与硬件片内测试,包含信道模块,误码统计模块,可设 2024-11-26 点击:20 评论:0

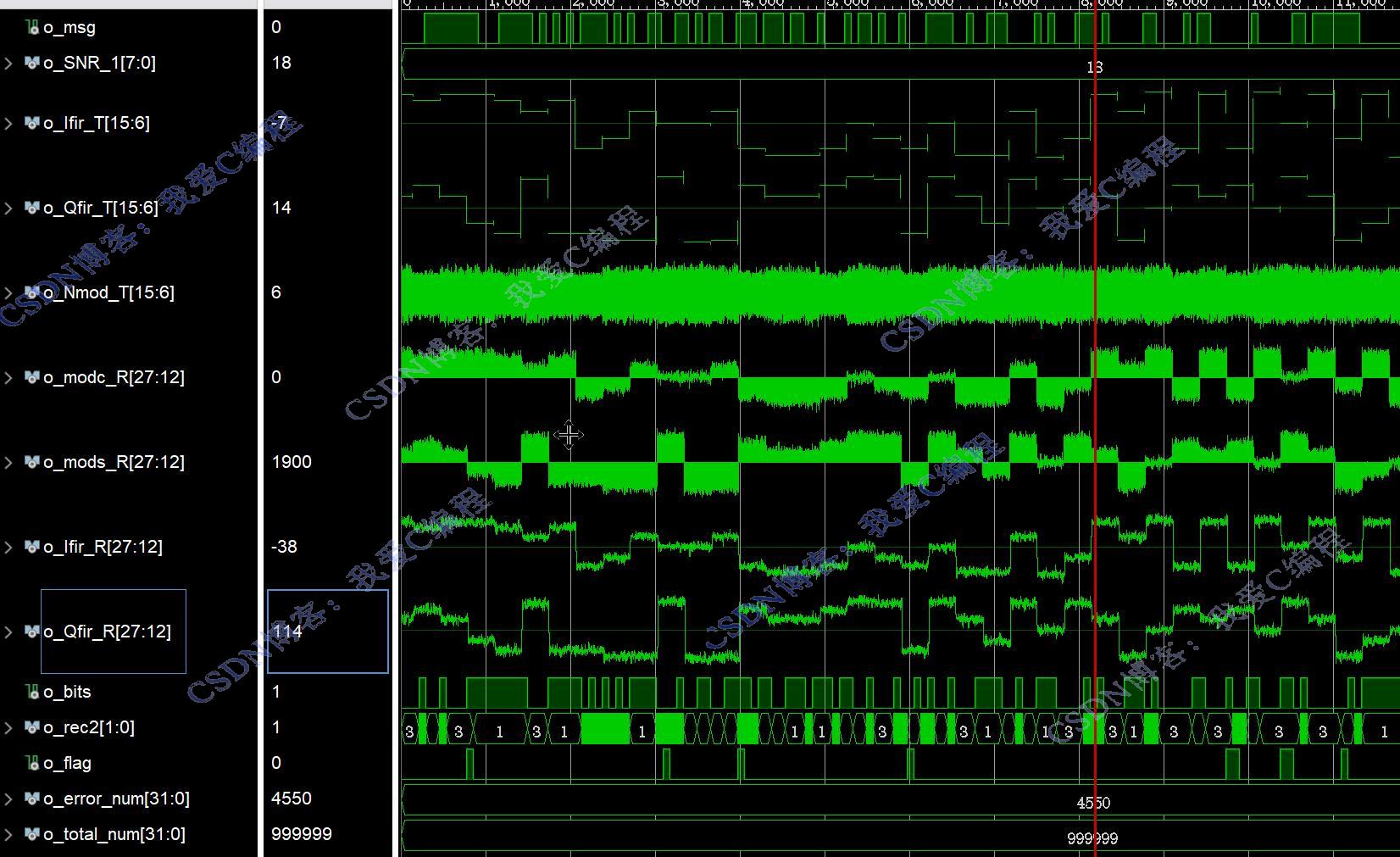

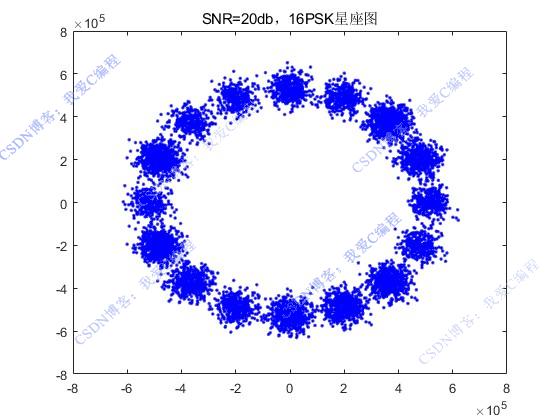

- 【硬件测试】基于FPGA的16psk调制解调系统开发与硬件片内测试,包含信道模块,误码统计模块,可设 2024-11-22 点击:18 评论:0

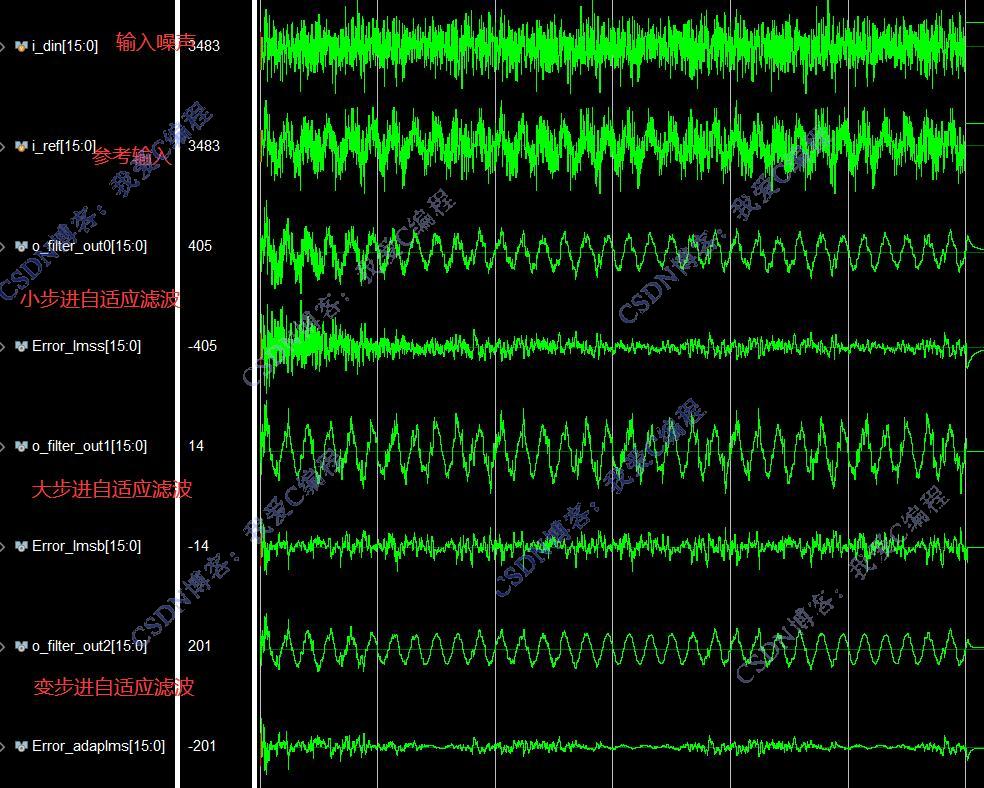

- 基于FPGA的变步长LMS自适应滤波器verilog实现,包括testbench 2024-11-20 点击:24 评论:0

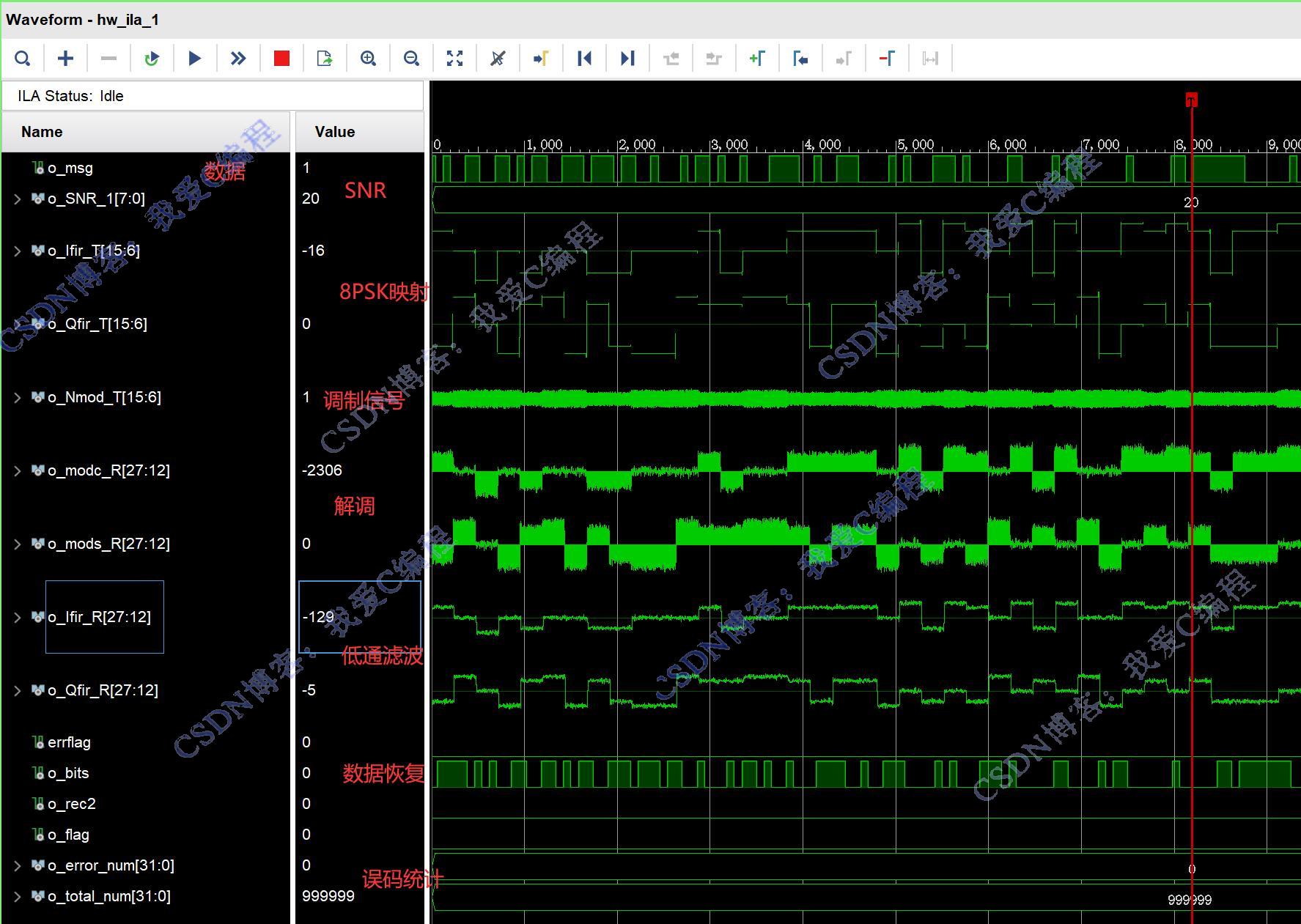

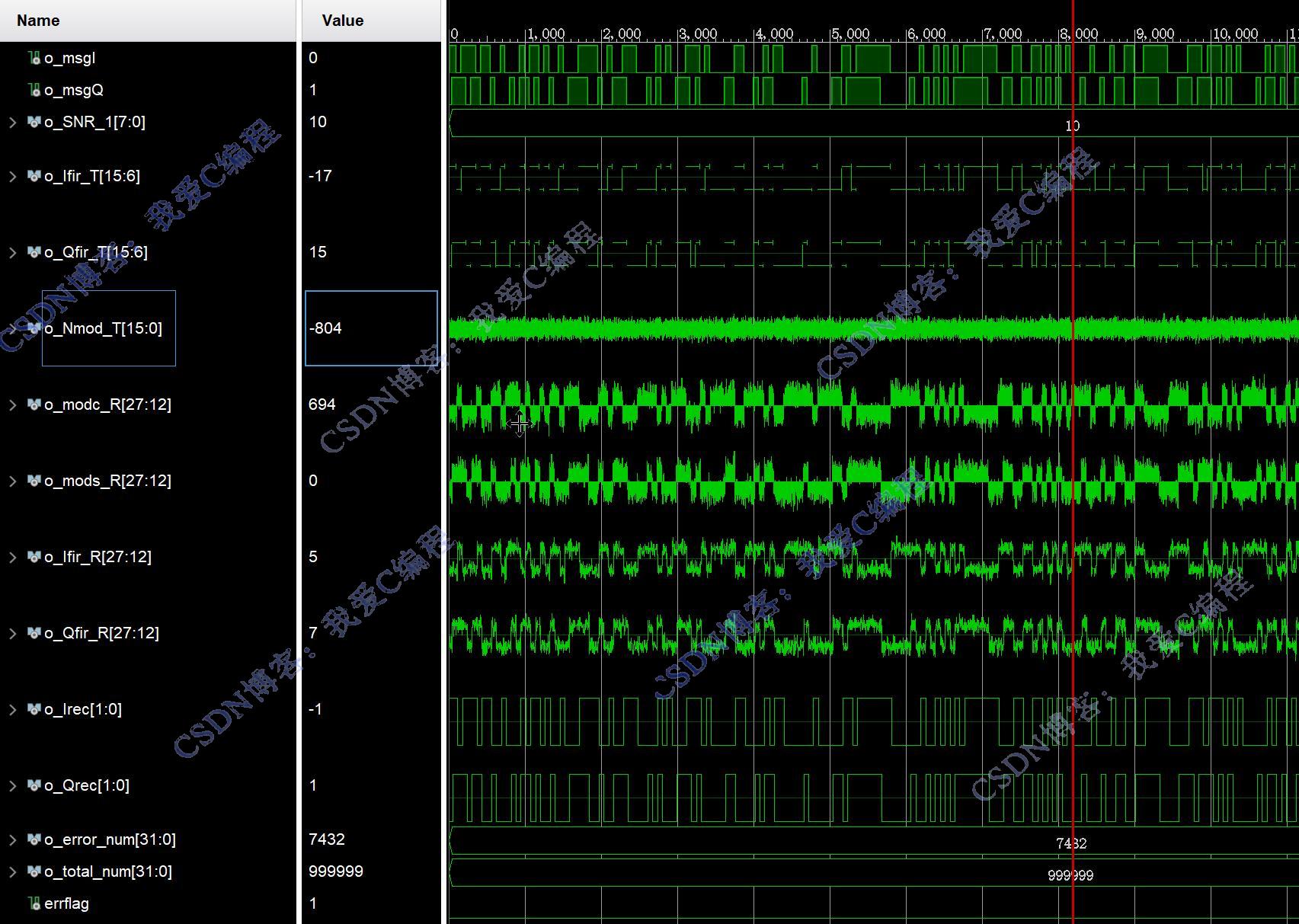

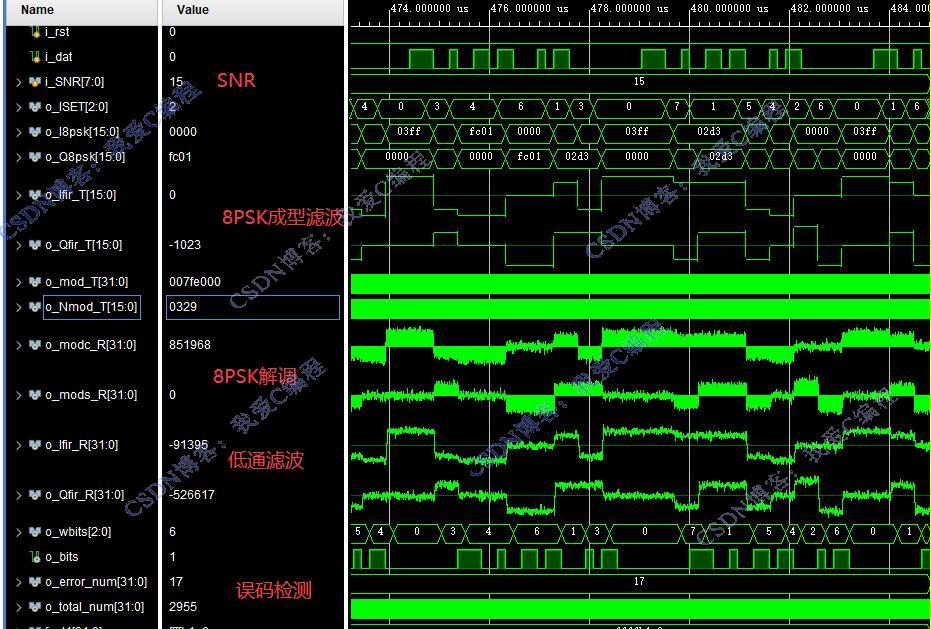

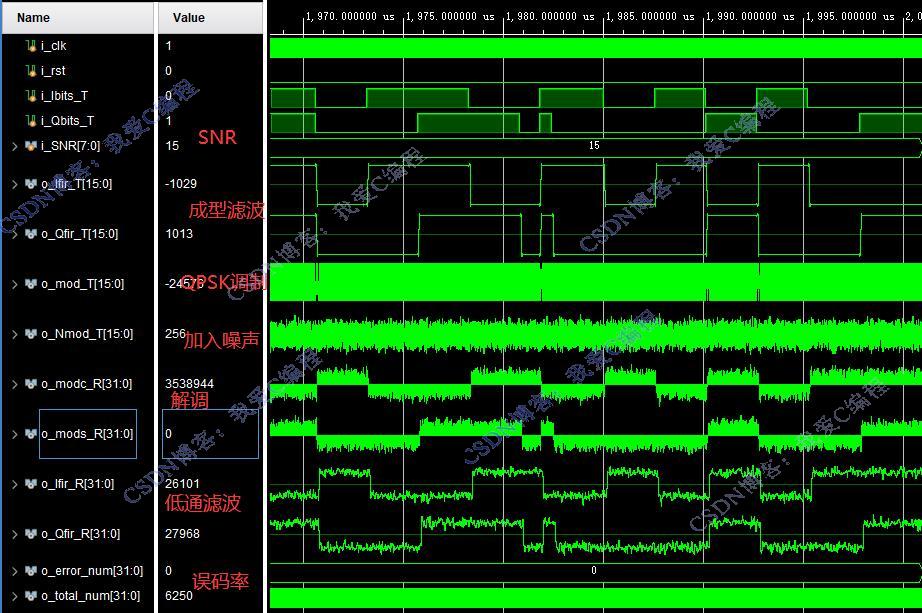

- 【硬件测试】基于FPGA的8PSK调制解调系统开发与硬件片内测试,包含信道模块,误码统计模块,可设置 2024-11-13 点击:21 评论:0

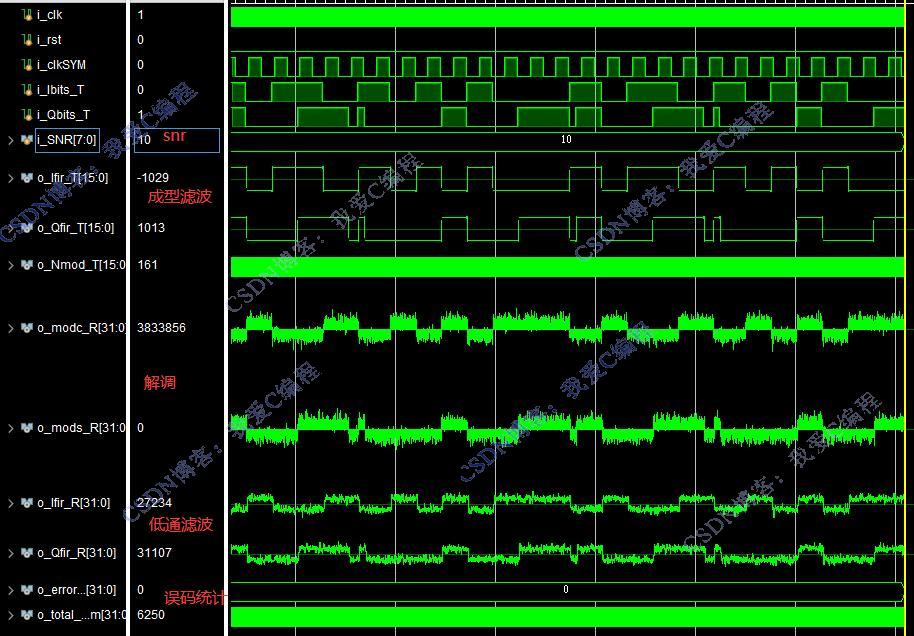

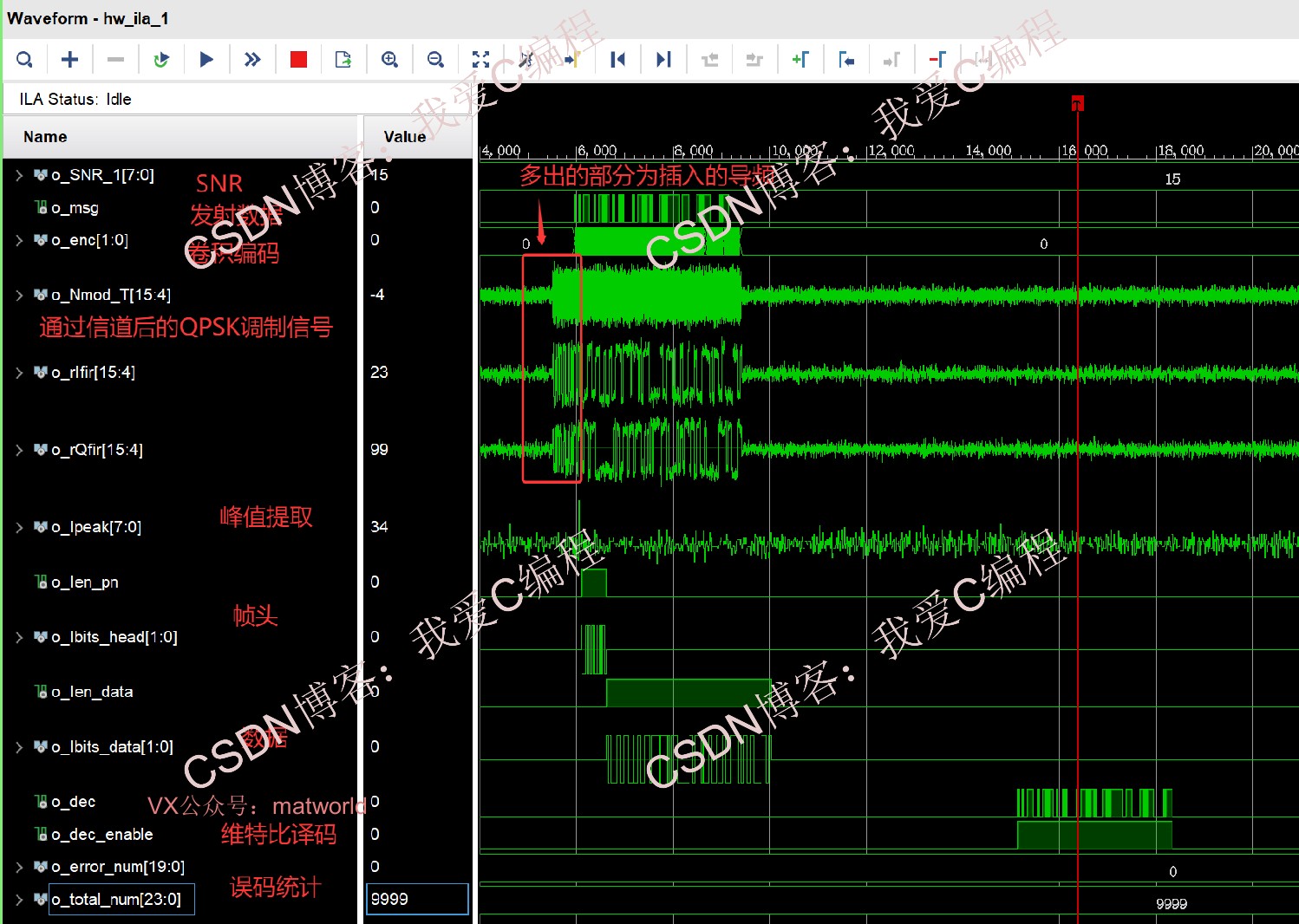

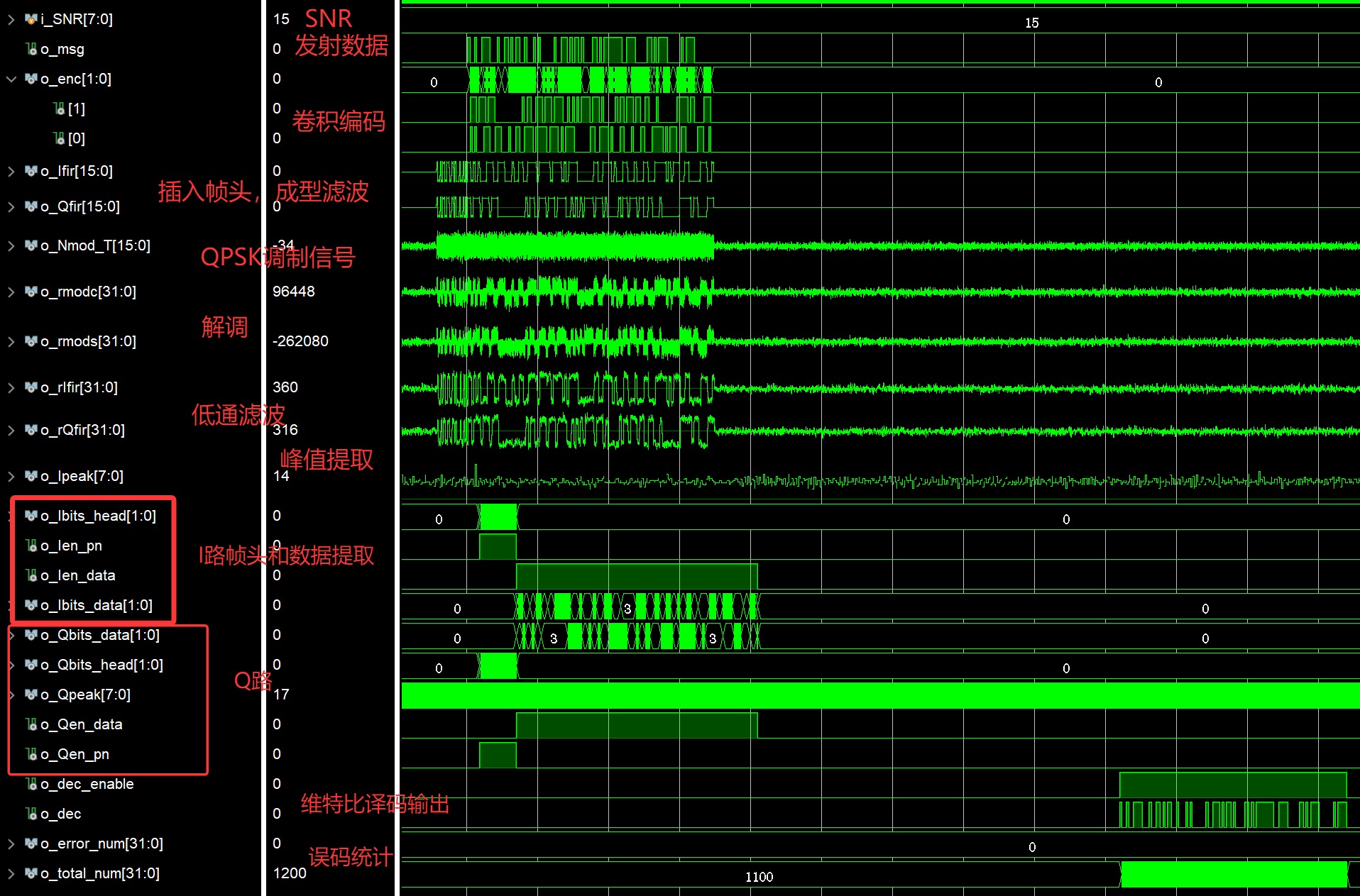

- 【硬件测试】基于FPGA的QPSK调制解调系统开发与硬件片内测试,包含信道模块,误码统计模块,可设置 2024-11-06 点击:20 评论:0

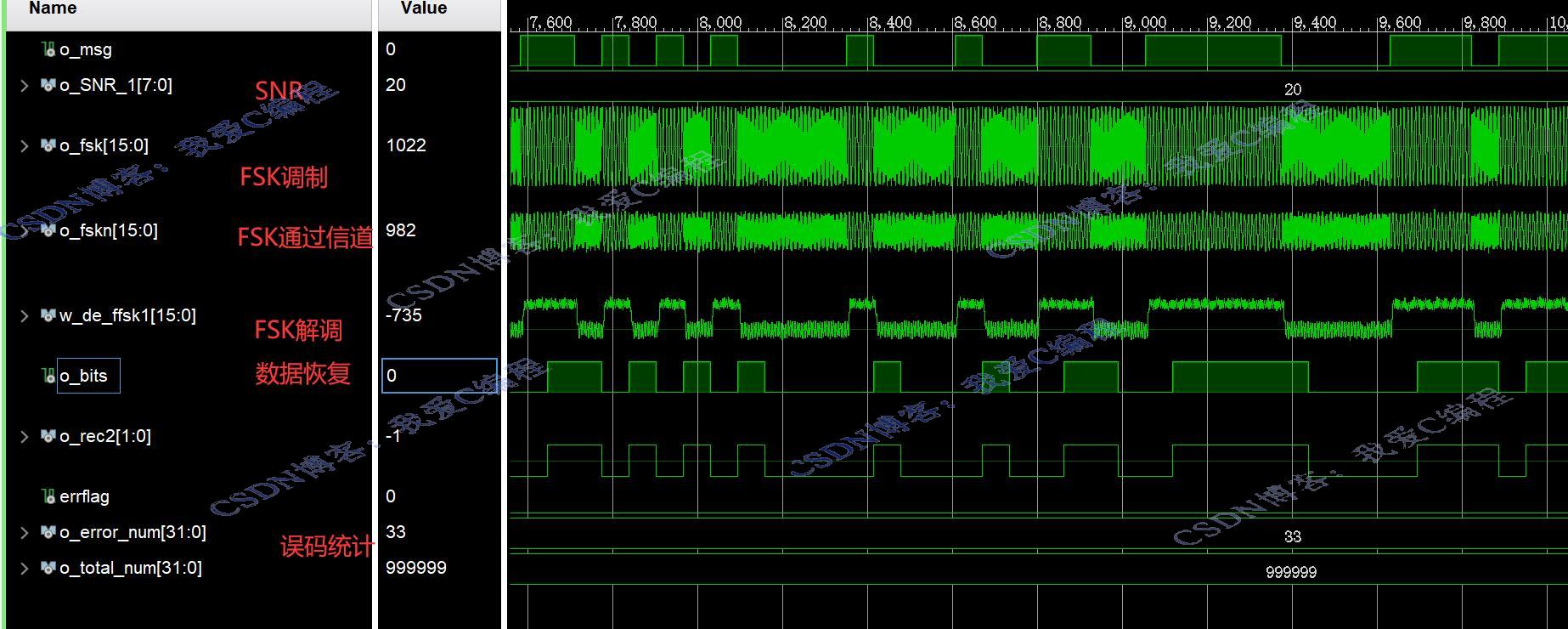

- 【硬件测试】基于FPGA的2FSK调制解调系统开发与硬件片内测试,包含信道模块,误码统计模块,可设置 2024-10-22 点击:21 评论:0

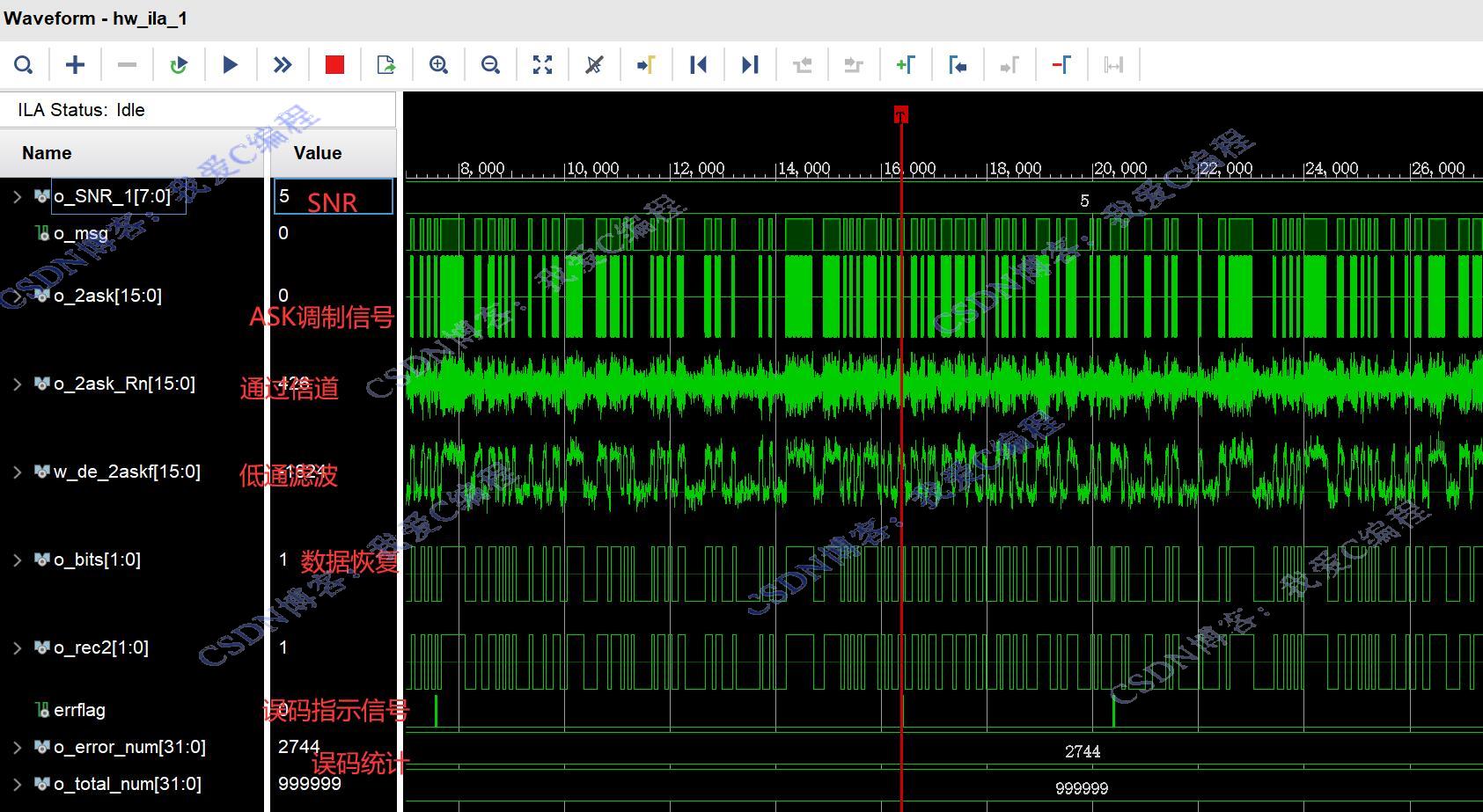

- 【硬件测试】基于FPGA的2ASK调制解调系统开发与硬件片内测试,包含信道模块,误码统计模块,可设置 2024-10-15 点击:22 评论:0

- 基于FPGA的16QAM调制+软解调系统,包含testbench,高斯信道模块,误码率统计模块,可以 2024-10-07 点击:24 评论:0

- 基于FPGA的QPSK调制+软解调系统,包含testbench,高斯信道模块,误码率统计模块,可以设 2024-10-07 点击:22 评论:0

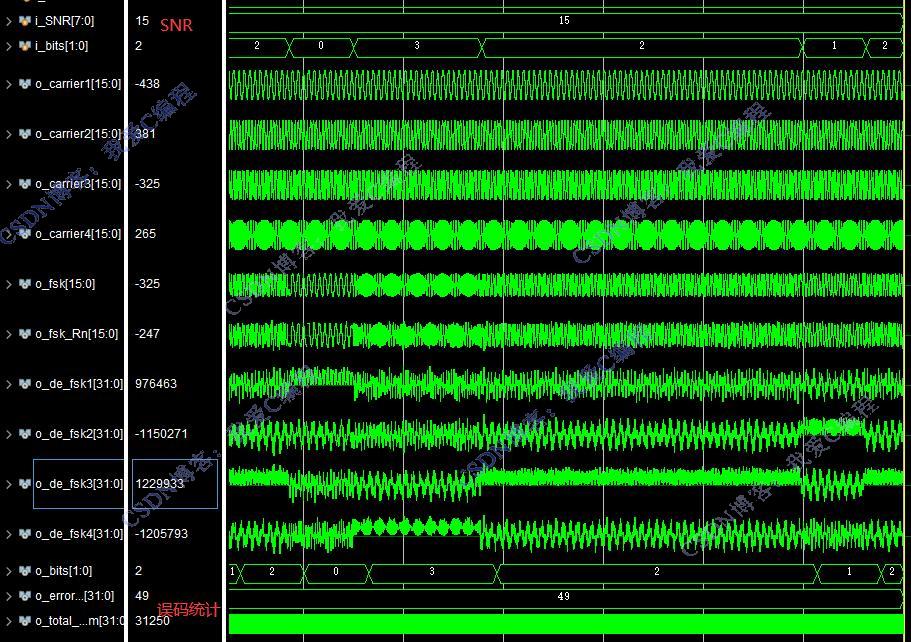

- 基于FPGA的4FSK调制解调系统,包含testbench,高斯信道模块,误码率统计模块,可以设置不 2024-09-30 点击:35 评论:0

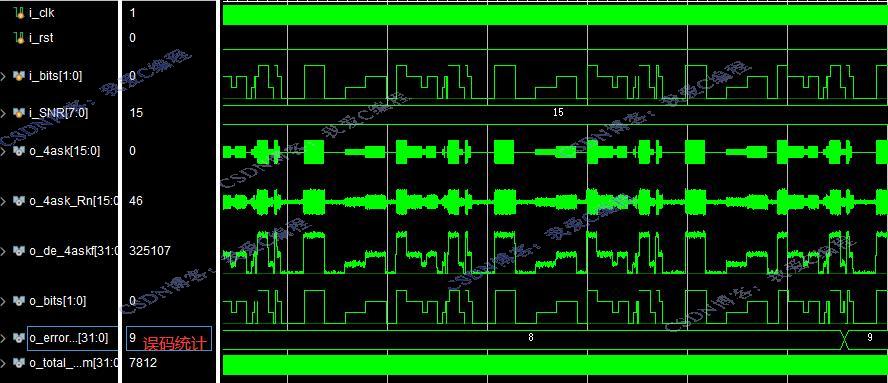

- 基于FPGA的4ASK调制解调系统,包含testbench,高斯信道模块,误码率统计模块,可以设置不 2024-09-27 点击:19 评论:0

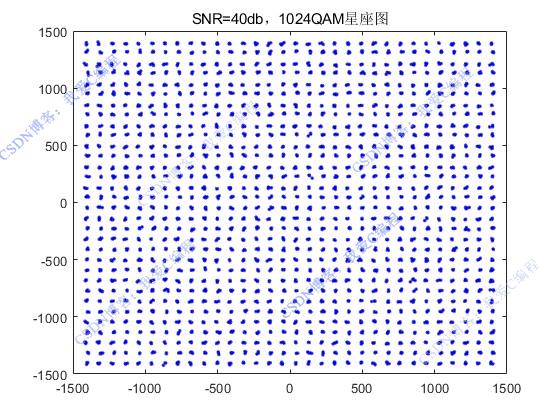

- 基于FPGA的1024QAM基带通信系统,包含testbench,高斯信道模块,误码率统计模块,可以 2024-09-16 点击:22 评论:0

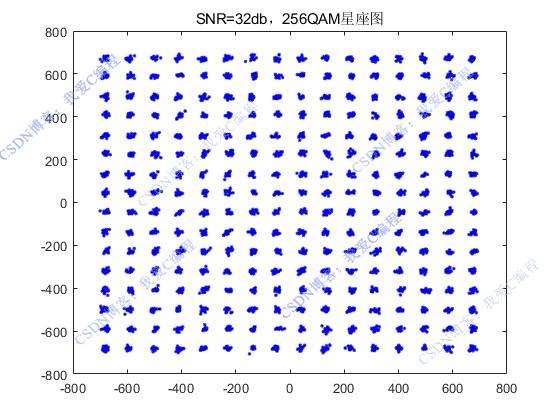

- 基于FPGA的256QAM基带通信系统,包含testbench,高斯信道模块,误码率统计模块,可以设 2024-09-07 点击:23 评论:0

- 基于FPGA的64QAM基带通信系统,包含testbench,高斯信道模块,误码率统计模块,可以设置 2024-09-01 点击:20 评论:0

- 基于FPGA的16QAM基带通信系统,包含testbench,高斯信道模块,误码率统计模块,可以设置 2024-08-25 点击:24 评论:0

- 基于FPGA的16PSK调制解调系统,包含testbench,高斯信道模块,误码率统计模块,可以设置 2024-08-14 点击:26 评论:0

- 基于FPGA的8PSK调制解调系统,包含testbench,高斯信道模块,误码率统计模块,可以设置不 2024-08-06 点击:28 评论:0

- 基于FPGA的QPSK调制解调系统,包含testbench,高斯信道模块,误码率统计模块,可以设置不 2024-07-27 点击:23 评论:0

0sj_036m,包括程序操作录像...

0sj_037m,包括程序操作录像...

0sj_033m,包括程序操作录像...

0sj_032m,包括程序操作录像...

0sj_031m,包括程序操作录像...

0sj_030m,包括程序操作录像+参考文献...

0sj_027m,包含操作步骤视频和参考文献...

0sj_025m,包括程序操作录像+参考文献...

0sj_023m,包括程序操作录像+说明文档...

0sj_020m,包括程序操作录像...

0sj_019m,包括程序操作录像...

0sj_018m,包括程序操作录像...

0sj_017m,包括程序操作录像...

0sj_015m,包括程序操作录像...

0sj_014m,包括程序操作录像...

0sj_013m...

0sj_012m...

0sj_010m,包括程序操作录像+参考文献...

0sj_008m,包括程序操作录像+参考文献...

0sj_007m,包括程序操作录像+参考文献...