1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/Z5WblZpp

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

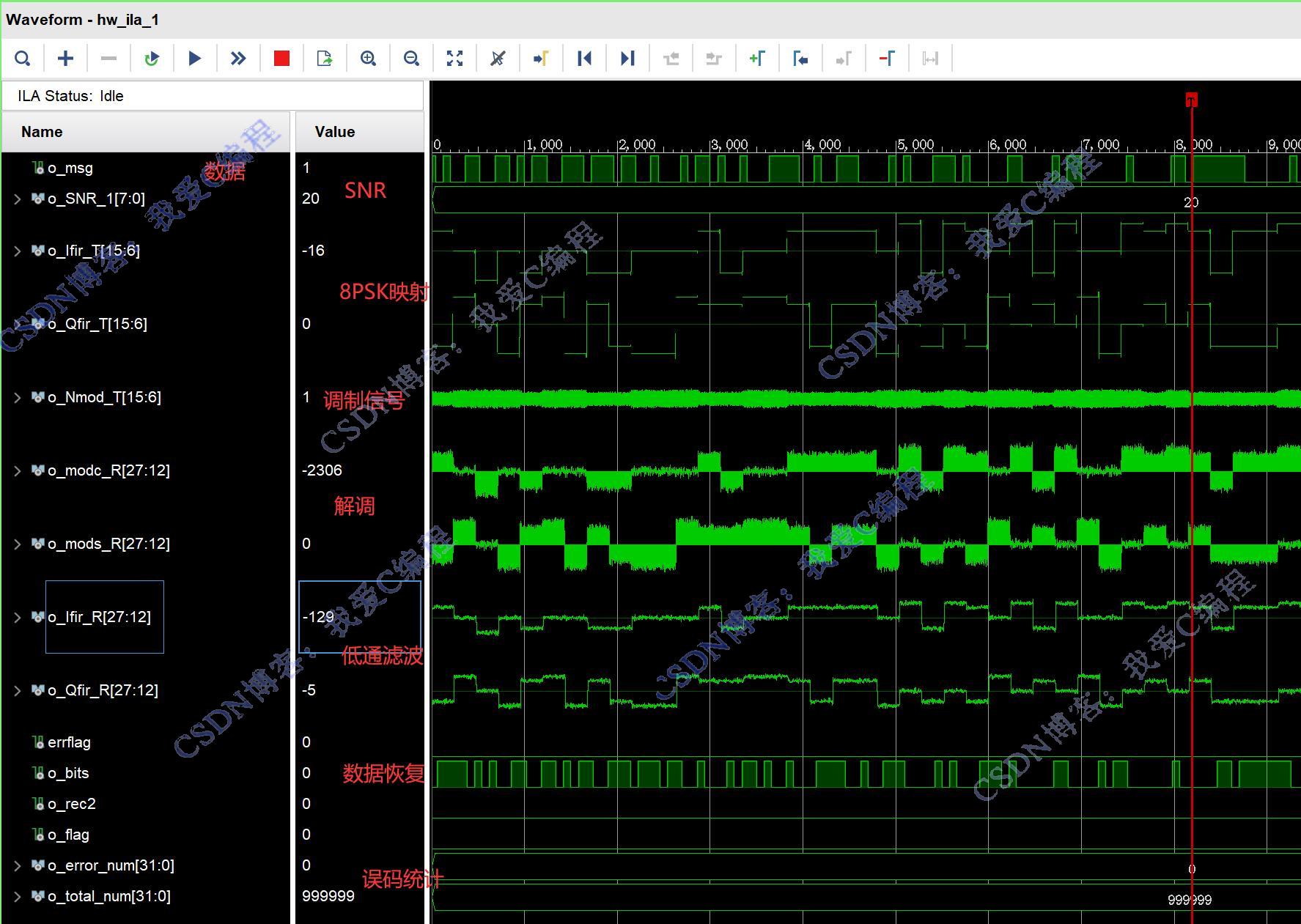

2.部分仿真图预览

3.算法概述

8PSK调制是一种相位调制方式,其基本原理是通过改变载波的相位来传递信息。在8PSK中,一个符号周期内的相位变化有8种可能的状态,分别对应3个比特的信息。因此,8PSK调制可以看作是一种将3个比特映射到一个符号的映射方式。具体地,假设输入的比特序列为b2b1b0,则对应的8PSK符号可以表示为:

S(t)=Acos(2πfct+θk) (1)

其中,A是载波的振幅,fc是载波的频率,θk是第k个符号的相位,k=0,1,...,7。θk的取值由输入的比特序列b2b1b0决定,具体的映射关系如表1所示。

4.部分源码

...................................................................

module tops_hdw(

input i_clk,

input i_rst,

output reg [3:0] led

);

wire o_msg;

//产生模拟测试数据

signal signal_u(

.i_clk (i_clk),

.i_rst (~i_rst),

.o_bits(o_msg)

);

//设置SNR

wire signed[7:0]o_SNR;

vio_0 your_instance_name (

.clk(i_clk), // input wire clk

.probe_out0(o_SNR) // output wire [7 : 0] probe_out0

);

wire[2:0]o_ISET;

wire signed[15:0]o_I8psk;

wire signed[15:0]o_Q8psk;

wire signed[15:0]o_Ifir_T;

wire signed[15:0]o_Qfir_T;

wire signed[31:0]o_mod_T;

wire signed[15:0]o_Nmod_T;

wire signed[31:0]o_modc_R;

wire signed[31:0]o_mods_R;

wire signed[31:0]o_Ifir_R;

wire signed[31:0]o_Qfir_R;

wire [2:0]o_wbits;

wire o_bits;

wire signed[31:0]o_error_num;

wire signed[31:0]o_total_num;

TOPS_8PSK TOPS_8PSK_u(

.i_clk (i_clk),

.i_rst (~i_rst),

.i_SNR (o_SNR),

.i_dat (o_msg),

.o_ISET (o_ISET),

.o_I8psk(o_I8psk),

.o_Q8psk(o_Q8psk),

.o_Ifir_T (o_Ifir_T),

.o_Qfir_T (o_Qfir_T),

.o_mod_T (o_mod_T),

.o_Nmod_T(o_Nmod_T),

.o_modc_R (o_modc_R),

.o_mods_R (o_mods_R),

.o_Ifir_R (o_Ifir_R),

.o_Qfir_R (o_Qfir_R),

.o_wbits(o_wbits),

.o_bits (o_bits),

.o_error_num(o_error_num),

.o_total_num(o_total_num),

.o_flag(o_flag)

);

//ila篇内测试分析模块

ila_1 ila_u (

.clk(i_clk), // input wire clk

.probe0({

o_msg,o_SNR,//9

o_Ifir_T[15:6], o_Qfir_T[15:6],o_Nmod_T[15:6],//36

o_modc_R[27:12],o_mods_R[27:12],o_Ifir_R[27:12],o_Qfir_R[27:12],//64

o_bits,

o_error_num,o_total_num,errflag,//64

o_rec2,o_flag

})

);

endmodule

0sj_030m

---