1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/Z5WXmZhw

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

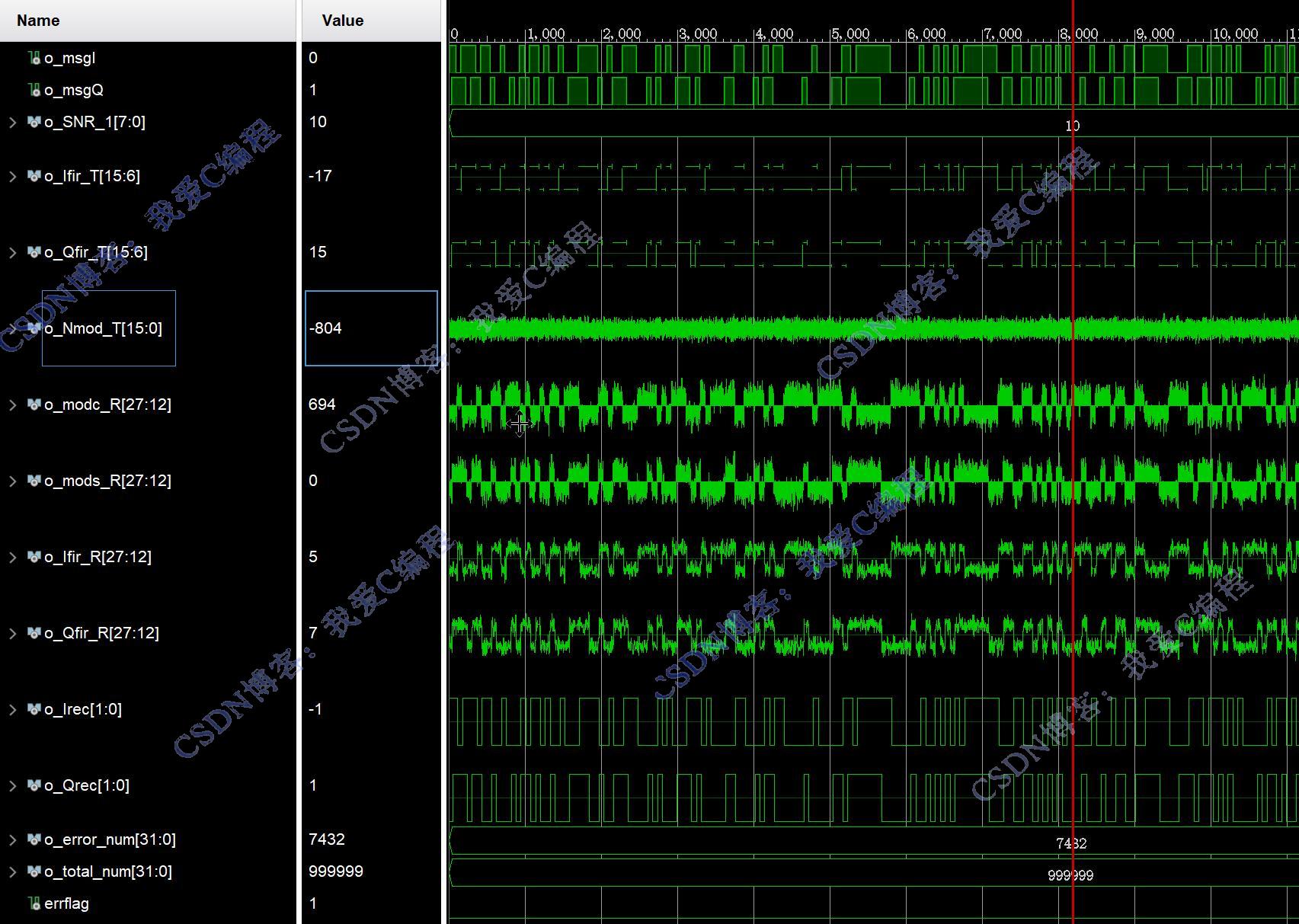

2.部分仿真图预览

3.算法概述

QPSK是一种数字调制方式,它将两个二进制比特映射到一个符号上,使得每个符号代表四种可能的相位状态。因此,QPSK调制解调系统可以实现更高的传输速率和更高的频谱效率。基于FPGA的QPSK调制解调系统通常由以下几个模块组成:数据生成模块:生成要传输的二进制数据流。

4.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/11/04 19:54:30

// Design Name:

// Module Name: tops_hdw

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tops_hdw(

input i_clk,

input i_rst,

output reg [3:0] led

);

wire o_msgI;

wire o_msgQ;

//产生模拟测试数据

signal signal_u(

.i_clk (i_clk),

.i_rst (~i_rst),

.o_bitsI(o_msgI),

.o_bitsQ(o_msgQ)

);

//设置SNR

wire signed[7:0]o_SNR;

vio_0 your_instance_name (

.clk(i_clk), // input wire clk

.probe_out0(o_SNR) // output wire [7 : 0] probe_out0

);

wire signed[15:0]o_Ifir_T;

wire signed[15:0]o_Qfir_T;

wire signed[31:0]o_mod_T;

wire signed[15:0]o_Nmod_T;

wire signed[31:0]o_modc_R;

wire signed[31:0]o_mods_R;

wire signed[31:0]o_Ifir_R;

wire signed[31:0]o_Qfir_R;

wire signed[31:0]o_error_num;

wire signed[31:0]o_total_num;

wire [1:0]o_Irec;

wire [1:0]o_Qrec;

wire errflag;

QPSK_tops QPSK_tops_u(

.i_clk (i_clk),

.i_rst (~i_rst),

.i_Ibits(o_msgI),

.i_Qbits(o_msgQ),

.i_SNR (o_SNR),

.o_Ifir (o_Ifir_T),

.o_Qfir (o_Qfir_T),

.o_mod_T(o_mod_T),

.o_Nmod_T(o_Nmod_T),

.o_modc (o_modc_R),

.o_mods (o_mods_R),

.o_rIfir (o_Ifir_R),

.o_rQfir (o_Qfir_R),

.o_error_num (o_error_num),

.o_total_num (o_total_num),

.o_Irec(o_Irec),

.o_Qrec(o_Qrec),

.o_flag(errflag)

);

//ila篇内测试分析模块

ila_0 ila_u (

.clk(i_clk), // input wire clk

.probe0({

o_msgI,o_msgQ,o_SNR,o_Ifir_T[15:6],o_Qfir_T[15:6],//30

o_Nmod_T,o_modc_R[27:12],o_mods_R[27:12],o_Ifir_R[27:12],o_Qfir_R[27:12],//75

o_error_num,o_total_num,errflag,//65

o_Irec,o_Qrec//4

})

);

endmodule

0sj_027m

---