1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/Z5iYmJpp

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

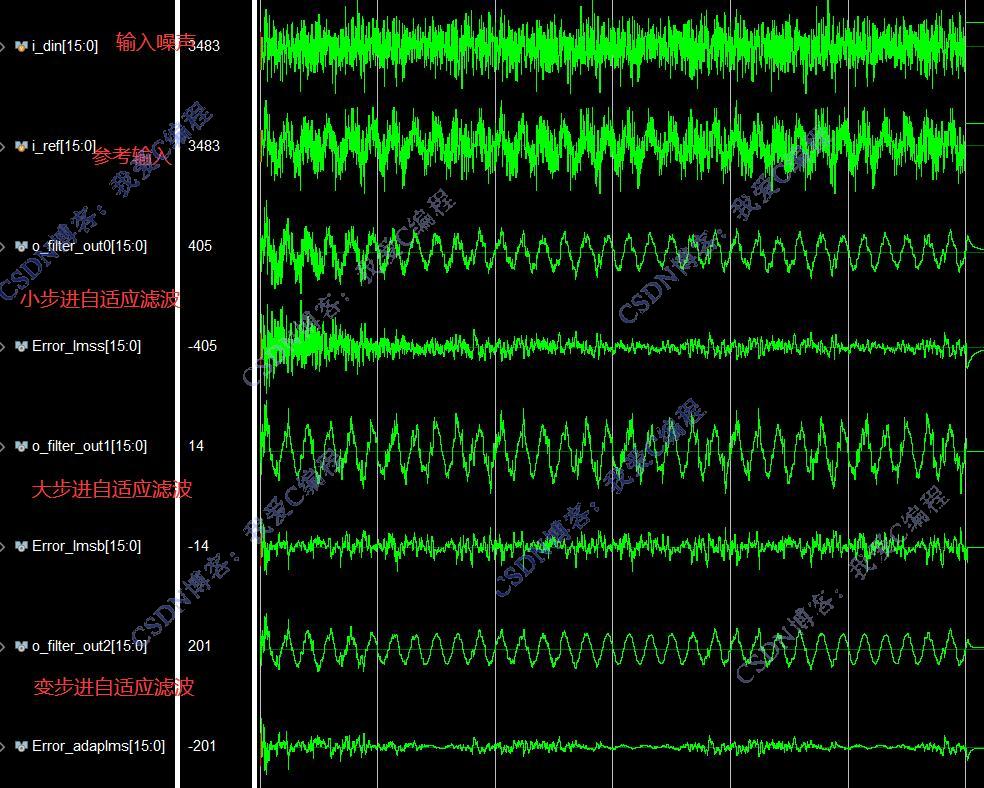

2.部分仿真图预览

3.算法概述

自适应滤波器在信号处理领域有着广泛的应用,如通信中的信道均衡、噪声消除、系统辨识等。最小均方(Least Mean Square,LMS)算法是一种经典的自适应滤波算法,因其简单易实现而备受关注。基于现场可编程门阵列(Field Programmable Gate Array,FPGA)实现变步长 LMS 自适应滤波器,可以充分利用 FPGA 的并行处理能力和可重构性,提高滤波器的性能和灵活性。

4.部分源码

`timescale 1ns / 1ps

module adap_lms(

input i_clk,

input i_rst,

input i_en,

input signed [15:0]i_din,

input signed [15:0]i_ref,

output signed [15:0]o_filter_out

);

.......................................................................

wire signed [15:0] Error_in,Data_in_reg,Desired_in_reg,Product_16;

wire signed [31:0] Product_32,LMSx8_sum_out;

Delay1clk Delay1clkU1 (

.i_clk (i_clk),

.i_rst (i_rst),

.i_en (i_en),

.i_din (i_din),

.o_dout (Data_in_reg)

);

Delay1clk Delay1clkU2 (

.i_clk (i_clk),

.i_rst (i_rst),

.i_en (i_en),

.i_din (i_ref),

.o_dout (Desired_in_reg)

);

assign Product_32 = r_Step * Error_in;

assign Product_16 = Product_32[26:11];

LMSs LMSsU(

.i_clk (i_clk),

.i_rst (i_rst),

.i_en (i_en),

.i_din (Data_in_reg),

.i_Step (Product_16),

.i_Sum (32'h0000_0000),

.o_Sum (LMSx8_sum_out)

);

assign Error_in = Desired_in_reg - LMSx8_sum_out[26:11];

Delay1clk Delay1clku3 (

.i_clk (i_clk),

.i_rst (i_rst),

.i_en (i_en),

.i_din (Error_in),

.o_dout (o_filter_out)

);

endmodule

0sj_031m

---