1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJucl5Zr

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

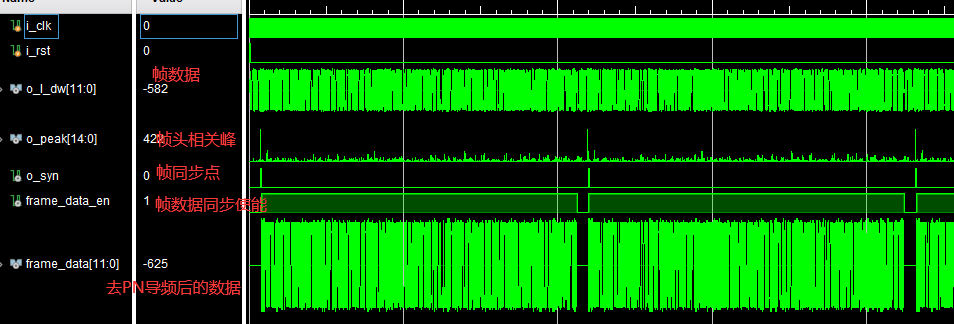

2.部分仿真图预览

3.算法概述

在数据通信系统中,数据帧检测与帧同步是一项重要的任务,用于确定数据传输中数据帧的起始位置和边界,以正确解析数据。基于PN(Pseudo-Noise)序列的帧同步技术是一种常用的实现方法,它通过检测PN序列在接收信号中的匹配来实现帧同步。

4.部分源码

module PN_1_sycn(

i_clk,

i_rst,

o_I_dw,

o_peak,

o_syn,

frame_data_en,

frame_data

);

input i_clk;

input i_rst;

output signed[11:0]o_I_dw;

output signed[14:0]o_peak ;

output o_syn;

output frame_data_en;

output signed[11:0]frame_data;

//测试信号

signal_gen signal_gen_u(

.i_clk (i_clk),

.i_rst (i_rst),

.o_I_dw(o_I_dw)

);

//帧同步

//峰值计算

wire signed[29:0]w_peak2;

peak_cal peak_cal_cal_u1(

.i_clk (i_clk),

.i_rst (i_rst),

.i_base_signal(o_I_dw[11:4]),

.o_peak (),

.o_peak2 (w_peak2)

);

assign o_peak= w_peak2[23:8];

//峰值检测,输出帧同步使能信号

//峰值定位,包括阈值判决粗同步和峰值最大值定位精同步

frame_syn frame_syn_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_lvl (16'd3000),

.i_peak ({o_peak}),

.o_syn (o_syn)

);

...........................................................................

assign frame_data=(frame_data_en==1'b1)?dly_dat[12]:12'd0;

endmodule

00_029m

---