1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/Z56Wmphs

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

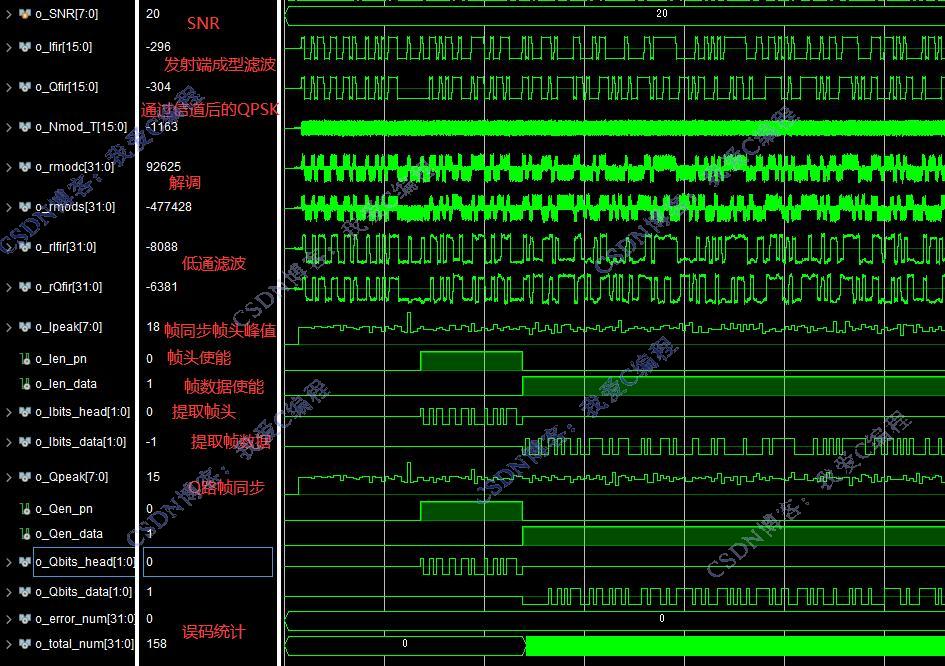

2.部分仿真图预览

3.算法概述

在数字通信中,信息通常是以帧为单位进行组织和传输的。帧同步的目的是确定每一帧的起始位置,以便接收端能够正确地解调出每帧中的数据。

设发送的帧结构为:帧同步码 + 信息码元序列 。帧同步码是具有特定规律的码序列,用于接收端识别帧的起始。

帧同步的过程就是在接收序列中寻找与帧同步码匹配的位置,一旦找到匹配位置,就确定了帧的起始位置,后续的码元就可以按照帧结构进行正确的划分和处理。

4.部分源码

..................................................

//QPSK调制

TQPSK TQPSKU(

.i_clk (i_clk),

.i_rst (i_rst),

.i_Ibits(i_Ibits),

.i_Qbits(i_Qbits),

.o_Ifir (o_Ifir),

.o_Qfir (o_Qfir),

.o_cos (),

.o_sin (),

.o_modc (),

.o_mods (),

.o_mod (o_mod_T)

);

//加入信道

awgns awgns_u(

.i_clk(i_clk),

.i_rst(i_rst),

.i_SNR(i_SNR), //这个地方可以设置信噪比,数值大小从-10~50,

.i_din(o_mod_T[24:9] + o_mod_T[25:10]),

.o_noise(),

.o_dout(o_Nmod_T)

);

//QPSK解调

RQPSK RQPSKU(

.i_clk (i_clk),

.i_rst (i_rst),

.i_med (o_Nmod_T),

.o_cos (),

.o_sin (),

.o_modc (o_rmodc),

.o_mods (o_rmods),

.o_Ifir (o_rIfir),

.o_Qfir (o_rQfir),

.o_Ibits(),

.o_Qbits(),

.o_Ibits_data(o_Ibits_data),

.o_Ibits_head(o_Ibits_head),

.o_Ipeak(o_Ipeak),

.o_Ien_data(o_Ien_data),

.o_Ien_pn(o_Ien_pn),

.o_Iframe_start(o_Iframe_start),

.o_Qbits_data(o_Qbits_data),

.o_Qbits_head(o_Qbits_head),

.o_Qpeak(o_Qpeak),

.o_Qen_data(o_Qen_data),

.o_Qen_pn(o_Qen_pn),

.o_Qframe_start(o_Qframe_start)

);

//计算误码率

//I,Q两路分别计算,最后统计平均值作为误码率

//error calculate

wire [31:0]w_error_num1;

wire [31:0]w_error_num2;

Error_Chech Error_Chech_u1(

.i_clk(i_clk),

.i_rst(i_rst),

.i_trans({i_Ibits}),

.i_en_data(o_Ien_data),

.i_rec(o_Ibits_data),

.o_error_num(w_error_num1),

.o_total_num(),

.o_rec2 ()

);

//error calculate

Error_Chech Error_Chech_u2(

.i_clk(i_clk),

.i_rst(i_rst),

.i_trans({i_Qbits}),

.i_en_data(o_Qen_data),

.i_rec(o_Qbits_data),

.o_error_num(w_error_num2),

.o_total_num(o_total_num),

.o_rec2 ()

);

assign o_error_num={w_error_num1[31],w_error_num1[31:1]} + {w_error_num2[31],w_error_num2[31:1]} ;

endmodule

0sj_056m

---