1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJWYlp1x

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

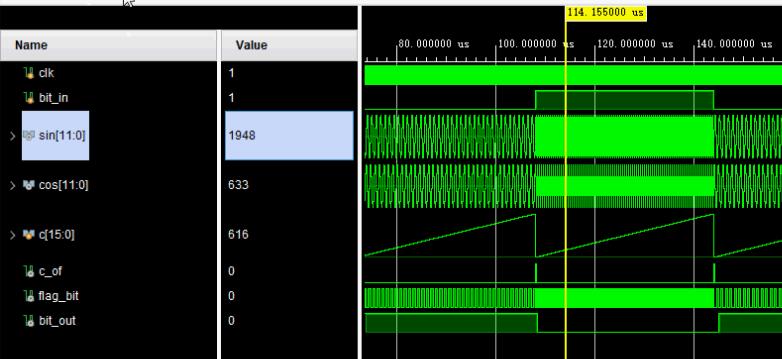

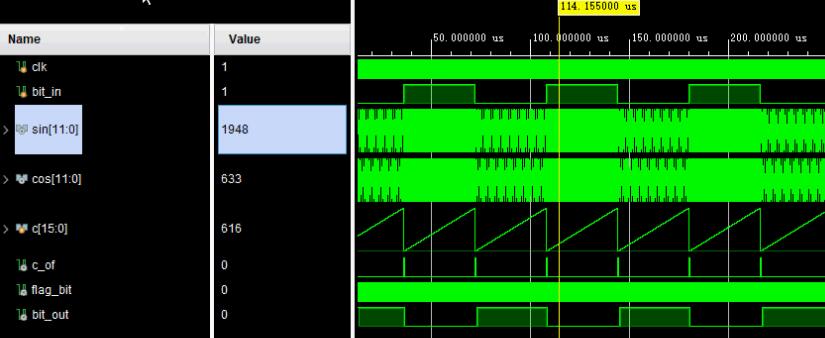

2.部分仿真图预览

3.算法概述

在二进制频移键控中,幅度恒定不变的载波信号的频率随着输入码流的变化而切换(称为高音和低音,代表二进制的1 和0)。产生FSK 信号最简单的方法是根据输入的数据比特是0还是1,在两个独立的振荡器中切换。采用这种方法产生的波形在切换的时刻相位是不连续的,因此这种FSK 信号称为不连续FSK 信号。由于相位的不连续会造频谱扩展,这种FSK 的调制方式在传统的通信设备中采用较多。随着数字处理技术的不断发展,越来越多地采用连继相位FSK调制技术。目前较常用产生FSK 信号的方法是,首先产生FSK 基带信号,利用基带信号对单一载波振荡器进行频率调制。相位连续的FSK信号的功率谱密度函数最终按照频率偏移的负四次幂衰落。如果相位不连续,功率谱密度函数按照频率偏移的负二次幂衰落。

4.部分源码

module FSK_modulator(

input bb_clk,

input bit_in ,

input [15:0] cnt0,cnt1,

input [7:0] step0,step1,

output reg [11:0] sin ,cos

);

wire [11:0] sin_w,cos_w;

always @(posedge bb_clk)sin<=sin_w;

always @(posedge bb_clk)cos<=cos_w;

wire [15:0] cnt0_w,cnt1_w ;

wire [7:0 ] step0_w,step1_w ;

.........................................................................

reg [15:0] cnt = 0;

reg [7:0] step = 0 ;

always@(posedge bb_clk) cnt <= ( bit_in ) ? cnt1_w : cnt0_w ;

always@(posedge bb_clk) step <= ( bit_in ) ? step1_w : step0_w ;

my_dds my_dds(.clk( bb_clk ) ,.rst( 1'b0 ) ,.clr ( 1'b0 ) ,.cnt( cnt) ,.step( step) ,.sin(sin_w ) ,.cos(cos_w ) );

endmodule

.........................................................................

module FSK_DEmodulator #(parameter SHORT_VALUE = 0 )(

input bb_clk,

output reg bit_out ,

input [15:0] v_short , v_long ,

input flag_bit

);

wire flag_bit_cross;

wire [15:0] v_short_w , v_long_w ;

.........................................................................

reg [15:0] c;always @ (posedge bb_clk)c <= (flag_bit_cross)?0:(c+1);

always @ (posedge bb_clk)if (flag_bit_cross)

begin if(c<v_short_w) bit_out <= SHORT_VALUE;else if (c>v_long_w)bit_out <= ~ SHORT_VALUE ;end

endmodule

A401