1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZZaXlZZt

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

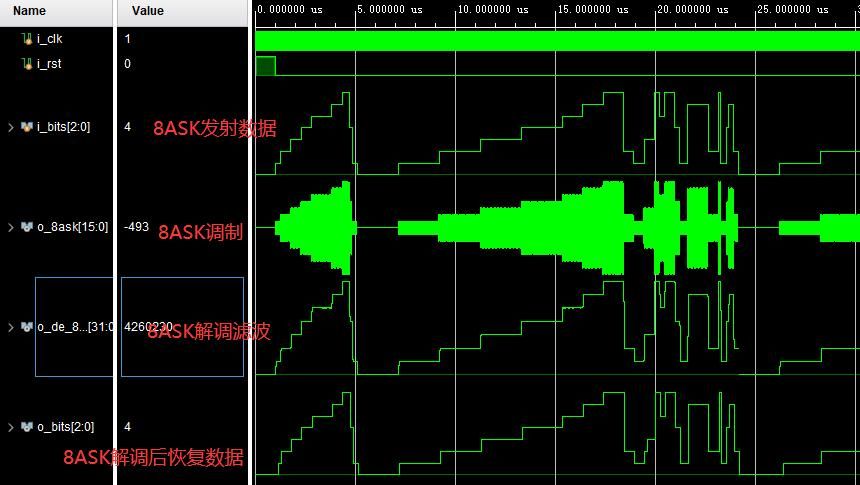

2.部分仿真图预览

3.算法概述

8ASK(八进制振幅键控)是一种数字调制技术,它是ASK(振幅键控)的一种扩展形式。在8ASK中,信号的振幅被调制成八个不同的级别,每个级别代表三个二进制位的信息。因此,与2ASK和4ASK相比,8ASK能够更高的提高数据传输效率。在8ASK调制中,二进制数据首先被编码为八进制的数字,然后通过改变载波的振幅来传递这些信息。不同的振幅级别对应不同的八进制数字,从而实现数据的传输。解调过程中,通过检测接收信号的振幅级别,可以还原出原始的二进制数据。

4.部分源码

`timescale 1ns / 1ps

//

//

module test_8ASK;

reg i_clk;

reg i_rst;

reg[2:0]i_bits;

wire signed[15:0]o_8ask;

wire signed[31:0]o_de_8askf;

wire [2:0]o_bits;

ASK8 uut(

.i_clk(i_clk),

.i_rst(i_rst),

.i_bits(i_bits),

.o_8ask(o_8ask),

.o_de_8ask(),

.o_de_8askf(o_de_8askf),

.o_bits(o_bits)

);

initial

begin

i_clk = 1'b1;

i_rst = 1'b1;

#1000

i_rst = 1'b0;

end

initial

begin

i_bits= 3'b000;

#1024

i_bits= 3'b001;

#256

i_bits= 3'b010;

#512

i_bits= 3'b011;

#512

i_bits= 3'b100;

#512

i_bits= 3'b101;

#1024

i_bits= 3'b110;

#512

i_bits= 3'b111;

#256

i_bits= 3'b111;

#128

i_bits= 3'b100;

#128

i_bits= 3'b001;

repeat(100)

begin

#256

i_bits= 3'b000;

#2048

i_bits= 3'b001;

#2048

i_bits= 3'b010;

#2048

i_bits= 3'b011;

#2048

i_bits= 3'b100;

#2048

i_bits= 3'b101;

#1024

i_bits= 3'b110;

#1024

i_bits= 3'b111;

#1024

i_bits= 3'b010;

#512

i_bits= 3'b001;

#512

i_bits= 3'b011;

#512

i_bits= 3'b111;

#256

i_bits= 3'b101;

#256

i_bits= 3'b111;

#512

i_bits= 3'b100;

#256

i_bits= 3'b001;

#128

i_bits= 3'b001;

#128

i_bits= 3'b001;

#128

i_bits= 3'b110;

#1024

i_bits= 3'b010;

#512

i_bits= 3'b111;

#128

i_bits= 3'b001;

#256

i_bits= 3'b100;

#128

i_bits= 3'b110;

#256

i_bits= 3'b010;

end

end

always #1 i_clk=~i_clk;

endmodule

00_051m

---