核心提示:01-115m含FPGA,详细文档及操作录像...

1.完整项目描述和程序获取

>面包多安全交易平台:

quartusii版本:https://mbd.pub/o/bread/Y5mUl59q

vivado版本:https://mbd.pub/o/bread/ZJiYkp9v

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

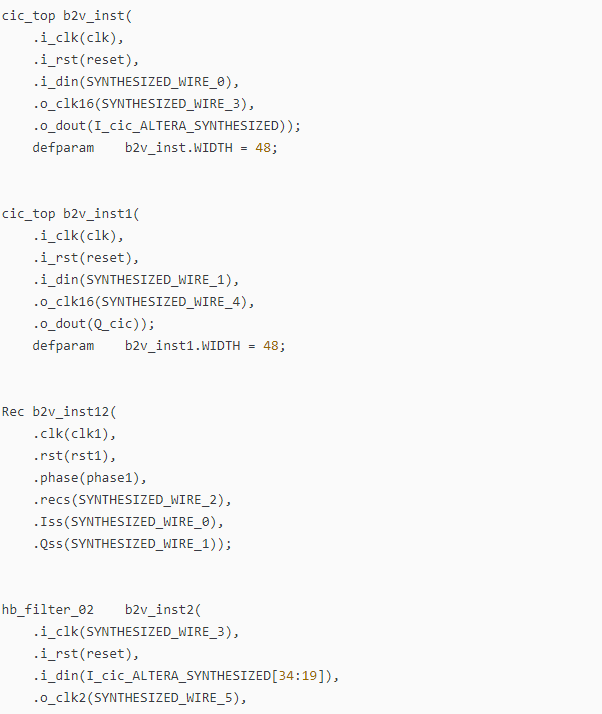

2.部分源码

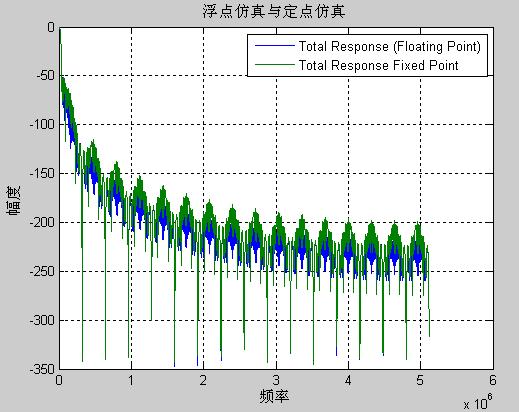

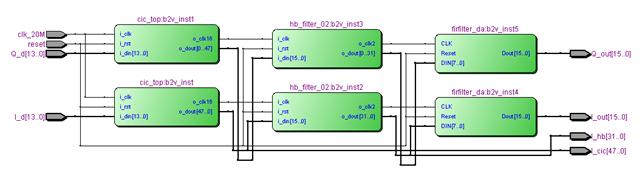

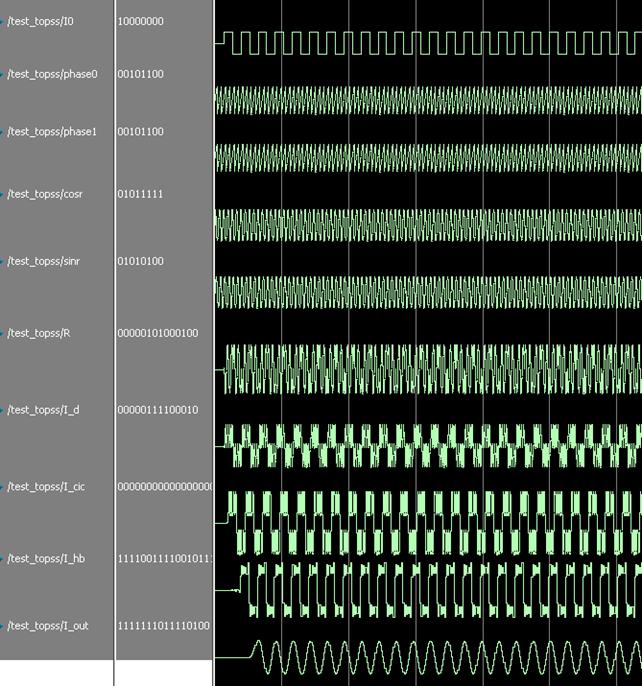

3.部分仿真图预览

4.算法概述

NCO使用CORDIC算法,CIC采用h结构的CIC滤波器,HBF采用复用结构的半带滤波器,而FIR则采用DA算法结构。

这里,我们首先假设不考虑中频信号输入的载波频偏问题,即发送的中频频率和本地的载波频率是一致的。

为了验证系统的正确性,我们首先需要设计一个发送源,由于你要求的信号带宽为20M,

所以整个系统我们设计的系统参数为,中频为80M,A/D采样为60M。本地接收端的载波频率为20M。

即发送端通过80M的中频调制之后,信号的频谱会搬移到80M附近,然后接收端通过AD60M采样后,会将频谱搬移到20M附近,且不会发生混叠现象。

那么系统测试方案可以简化为,一个中心频率在20M附近的中频输入测试信号进行测试。