核心提示:01_115m,包括程序操作录像+说明文档...

1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/Y5mUl5tv

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

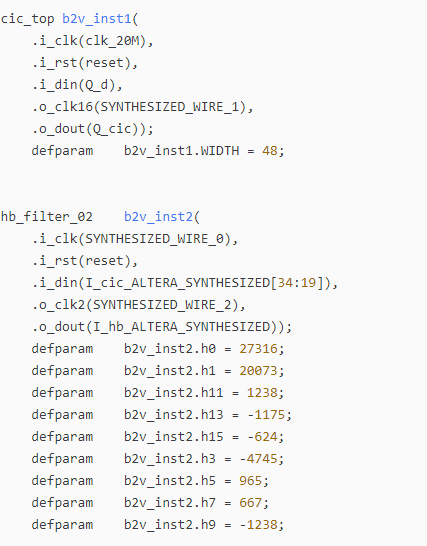

2.部分源码

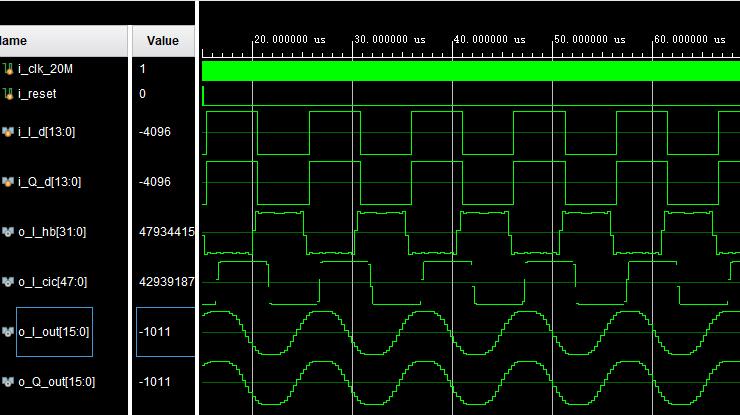

3.部分仿真图预览

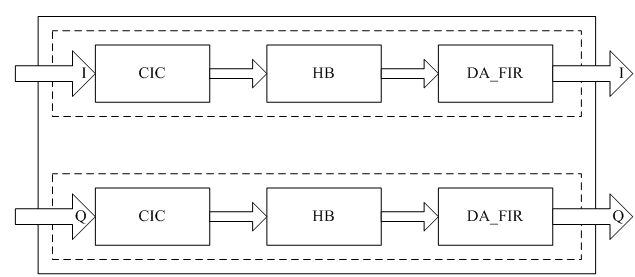

4.算法概述

数字下变频中的低通滤波器是由多级抽取滤波器组实现的。信号的同相分量和正交分量再分别经由积分梳状滤波器(CIC)、半带滤波器(HB)和有限长单位脉冲响应(FIR)滤波器构成的多级抽取滤波器组进行滤波和降采样处理,再将产生的正交基带信号I (n)、Q (n)送到通用DSP处理器,进行信号识别、解调等基带信号处理。