1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/Z52Xmpxt

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

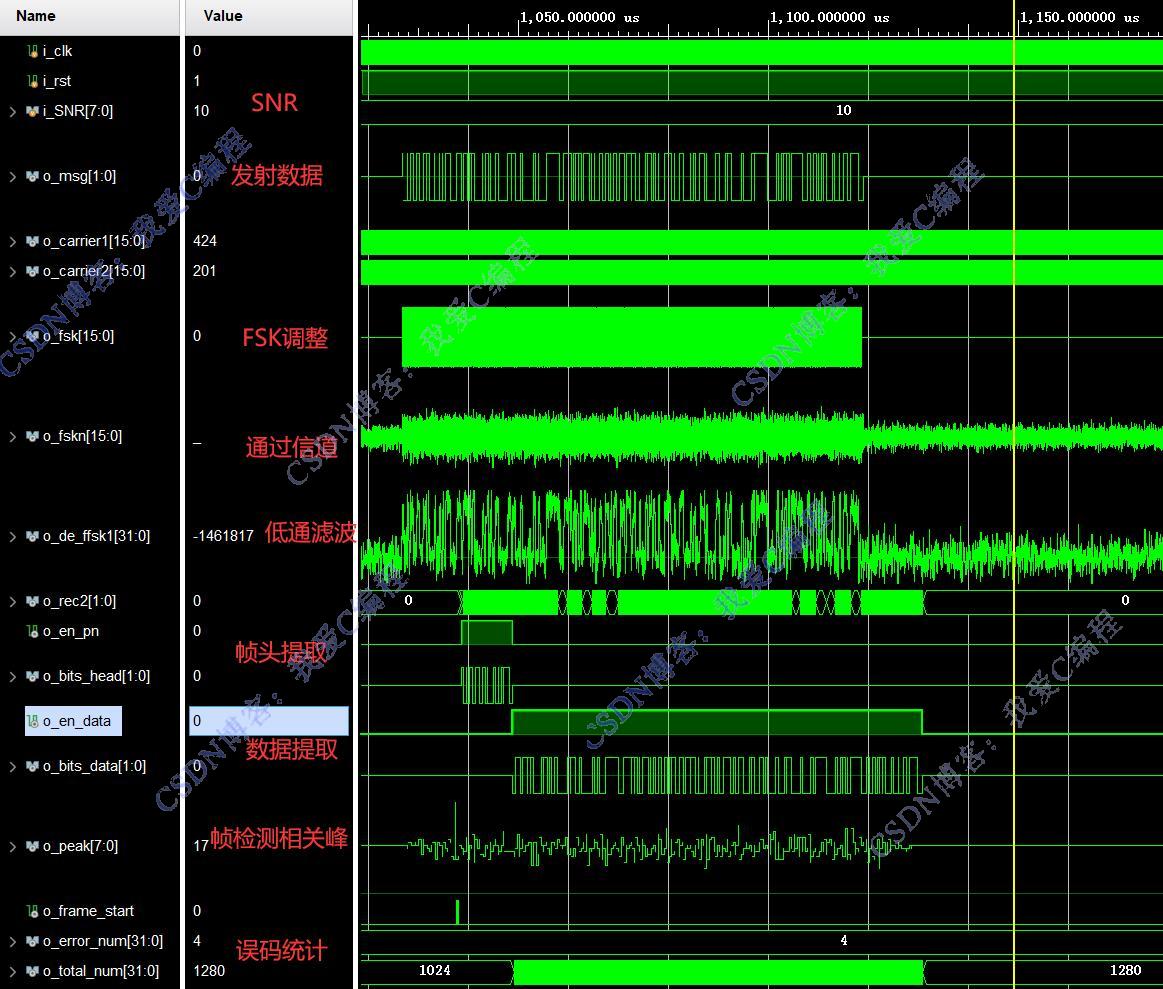

2.部分仿真图预览

3.算法概述

在二进制频移键控中,幅度恒定不变的载波信号的频率随着输入码流的变化而切换(称为高音和低音,代表二进制的1 和0)。产生FSK 信号最简单的方法是根据输入的数据比特是0还是1,在两个独立的振荡器中切换。采用这种方法产生的波形在切换的时刻相位是不连续的,因此这种FSK 信号称为不连续FSK 信号。

4.部分源码

....................................................................

//调制

FSK_mod FSK_mod_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_bits (i_bits),

.o_carrier1(o_carrier1),

.o_carrier2(o_carrier2),

.o_fsk (o_fsk)

);

awgns awgns_u(

.i_clk(i_clk),

.i_rst(i_rst),

.i_SNR(i_SNR), //这个地方可以设置信噪比,数值大小从-10~50,

.i_din(o_fsk),

.o_noise(),

.o_dout(o_fskn)

);

//解调

FSK_demod FSK_demod_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_fsk (o_fskn),

.o_de_fsk1 (),

.o_de_ffsk1 (o_de_ffsk1),

.o_bits (o_bits),

.o_bits_data (o_bits_data),

.o_bits_head (o_bits_head),

.o_peak (o_peak),

.o_en_data (o_en_data),

.o_en_pn (o_en_pn),

.o_frame_start (o_frame_start)

);

//error calculate

Error_Chech Error_Chech_u(

.i_clk(i_clk),

.i_rst(i_rst),

.i_trans(i_bits),

.i_en_data(o_en_data),

.i_rec(o_bits_data),

.o_error_num(o_error_num),

.o_total_num(o_total_num),

.o_rec2(o_rec2)

);

0sj_049m

endmodule

---