1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJuTlJZy

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

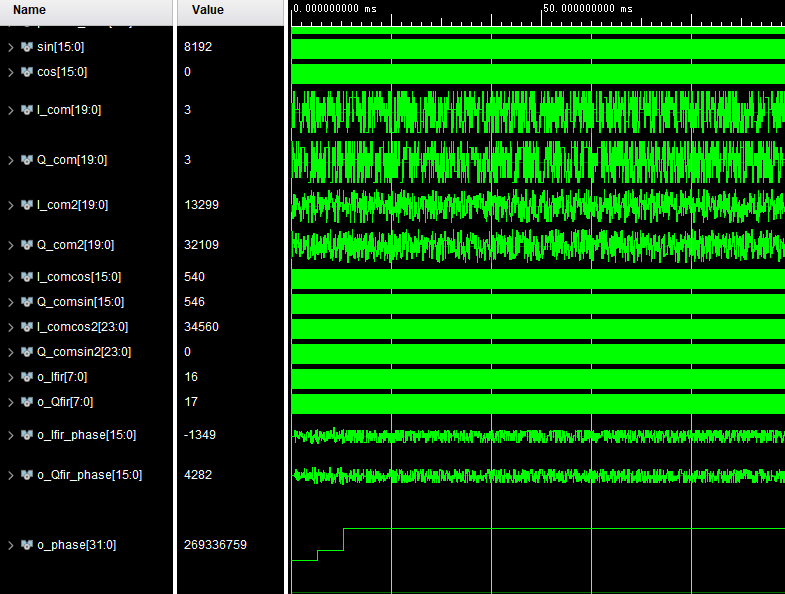

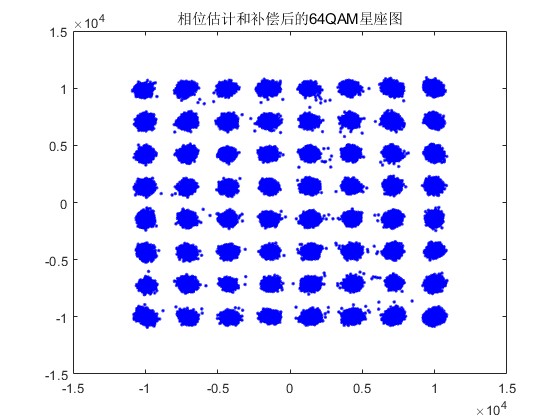

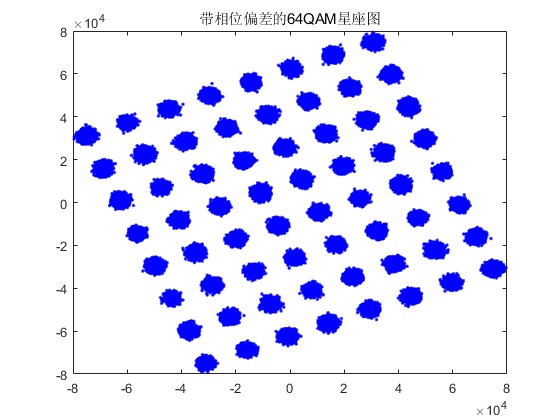

2.部分仿真图预览

3.算法概述

在现代通信系统中,调制技术是实现高速数据传输和频谱效率优化的重要手段。其中,64QAM调制技术是一种常见的高阶调制技术,可以实现每个符号传输6个比特的信息,从而提高数据传输速率。然而,在实际应用中,调制信号往往会受到各种干扰和失真的影响,导致传输错误率增加。因此,相位估计和补偿技术是调制信号解调和恢复的关键环节之一。

4.部分源码

...........................................................................

module TEST;

reg clk;

reg rst;

reg start;

wire [5:0] parallel_data;

wire [15:0]sin;

wire [15:0]cos;

wire signed[19:0] I_com;

wire signed[19:0] Q_com;

wire signed[19:0] I_com2;

wire signed[19:0] Q_com2;

wire signed[15:0]I_comcos;

wire signed[15:0]Q_comsin;

// DUT

tops_64QAM_mod top(

.clk(clk),

.rst(rst),

.start(start),

.parallel_data(parallel_data),

.sin(sin),

.cos(cos),

.I_com(I_com),

.Q_com(Q_com),

.I_com2(I_com2),

.Q_com2(Q_com2),

.I_comcos(I_comcos),

.Q_comsin(Q_comsin)

);

wire signed[23:0]I_comcos2;

wire signed[23:0]Q_comsin2;

wire signed[7:0]o_Ifir;

wire signed[7:0]o_Qfir;

wire signed[15:0]o_Ifir_phase;

wire signed[15:0]o_Qfir_phase;

wire signed[31:0]o_phase;

tops_64QAM_phase_est top2(

.clk(clk),

.rst(rst),

.start(start),

.I_comcos(I_comcos),

.Q_comsin(Q_comsin),

.I_comcos2(I_comcos2),

.Q_comsin2(Q_comsin2),

.o_Ifir(o_Ifir),

.o_Qfir(o_Qfir),

.o_I_phase(o_Ifir_phase),

.o_Q_phase(o_Qfir_phase),

.o_phase(o_phase)

);

initial begin

clk = 0;

rst = 0;

start = 1;

#10;

rst = 1;

end

always #5

clk <= ~clk;

reg writeen;

initial

begin

writeen = 1'b0;

#150000

writeen = 1'b1;

end

reg[4:0]divcnt;

always @(posedge clk or negedge rst)

begin

if(~rst)

begin

divcnt<={5{1'b0}};

end

else begin

divcnt<=divcnt+{5{1'b1}};

end

end

integer fout1;

integer fout2;

initial begin

fout1 = $fopen("It.txt","w");

fout2 = $fopen("Qt.txt","w");

end

always @ (posedge divcnt[4])

begin

if(writeen==1)

begin

$fwrite(fout1,"%d\n",I_com2);

$fwrite(fout2,"%d\n",Q_com2);

end

end

integer fout3;

integer fout4;

initial begin

fout3 = $fopen("IR.txt","w");

fout4 = $fopen("QR.txt","w");

end

always @ (posedge divcnt[4])

begin

if(writeen==1)

begin

$fwrite(fout3,"%d\n",o_Ifir_phase);

$fwrite(fout4,"%d\n",o_Qfir_phase);

end

end

endmodule

00_022m