1.完整项目描述和程序获取

>面包多安全交易平台

如果需要使用vivado平台开发,打开链接:https://mbd.pub/o/bread/ZJiVmppr

如果需要使用quartusii平台开发,打开链接:https://mbd.pub/o/bread/mbd-ZJiXkp5y

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

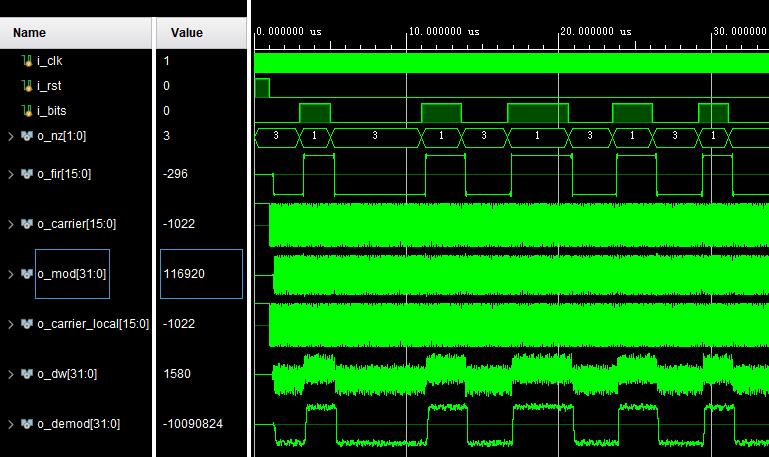

2.部分仿真图预览

3.算法概述

BPSK (Binary Phase Shift Keying)-------二进制相移键控。是把模拟信号转换成数据值的转换方式之一,利用偏离相位的复数波浪组合来表现信息键控移相方式。BPSK使用了基准的正弦波和相位反转的波浪,使一方为0,另一方为1,从而可以同时传送接受2值(1比特)的信息。

4.部分源码

..............................................................

//调制端

assign o_nz=(i_bits == 1'b1)?2'b01:2'b11;

wire[23:0]m_fir;

fir_compiler_0 uut (

.aresetn(~i_rst),

.aclk(i_clk),

.s_axis_data_tvalid(1'b1),

.s_axis_data_tready(),

.s_axis_data_tdata({o_nz[1],o_nz[1],o_nz[1],o_nz[1],o_nz[1],o_nz[1],o_nz}),

.m_axis_data_tvalid(),

.m_axis_data_tdata(m_fir)

);

assign o_fir=m_fir[23:8];

wire[31:0]m_carrier;

dds_compiler_0 uut2(

.aclk (i_clk),

.aresetn (~i_rst),

.s_axis_config_tvalid(1'b1),

.s_axis_config_tdata(32'd100000000),

.m_axis_data_tvalid(),

.m_axis_data_tdata(m_carrier),

.m_axis_phase_tvalid(),

.m_axis_phase_tdata()

);

assign o_carrier=m_carrier[15:0];

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

o_mod <= 32'd0;

end

else begin

o_mod <= $signed(o_carrier)*$signed(o_fir);

end

end

//解调端 ,不考虑载波同步

wire[31:0]m_carrier_local;

dds_compiler_0 uut3(

.aclk (i_clk),

.aresetn (~i_rst),

.s_axis_config_tvalid(1'b1),

.s_axis_config_tdata(32'd100000000),

.m_axis_data_tvalid(),

.m_axis_data_tdata(m_carrier_local),

.m_axis_phase_tvalid(),

.m_axis_phase_tdata()

);

assign o_carrier_local=m_carrier_local[15:0];

reg signed[31:0]tmps;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

tmps <= 32'd0;

end

else begin

tmps <= $signed(o_carrier_local)*$signed(o_mod[31:16]);

end

end

assign o_dw=tmps;

wire signed[31:0]tmps2;

fiter_rrc uut4(

.i_clk (i_clk),

.i_rst (i_rst),

.i_dat (tmps[20:5]),

.o_demod(o_demod)

);

endmodule

00_001m