1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJacmZZv

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

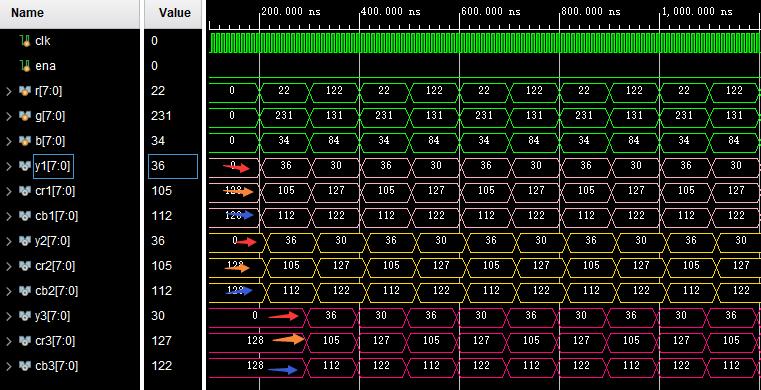

2.部分仿真图预览

3.算法概述

人类获得信息的主要方式是视觉,通常情况下颜色有2种描述方式,一种是RGB色度空间表示,一种是 YCbCr色度空间表示。然而,普通的R GB颜色空间对视频的显示存在很多问题,将其转换为YCbCr颜色空间能够很 好地适应现代社会的要求,本文正是采用一种新的方法,通过FPGA成功地将其转化,并得到正确的结果,此方法内 部变量少、算法优点突出、实时性好,十分易于在实际工程中实现。

RGB颜色空间

在RGB颜色空间中,1个带颜色的图像采样是用3个 值来表示一个像素点的相对的红、绿和蓝色比(3种光线的 主样构成颜色)。任何颜色都可以通过把红、绿和蓝通过 不同的比例相混得到。CRT和LCD通过分别对每个像素 点的红绿蓝值进行显示来得到各种颜色。从一个通常的观

察距离来看,不同的构成部分可以达到颜色上的真实感。

YCbCr颜色空间

人类视觉系统(HVS)相比亮度来说对于颜色不是那 么敏感。在RGB颜色空间中,3种颜色被平等地看待,并 用相同的分辨率存放起来。但是通过把亮度与颜色信息 分离,并对亮度值取更高的分辨率可以更有效地表示1个 颜色图像。

4.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/03/26 18:01:20

// Design Name:

// Module Name: tops

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tops(

clk,

ena,

r,

g,

b,

y,

cr,

cb

);

input clk;//输入时钟

input ena;//输入使能信号

input[7:0]r; //输入R,G,B信号

input[7:0]g;

input[7:0]b;

output[7:0]y;//输出Y,CR,CB信号

output[7:0]cr;

output[7:0]cb;

//mult your_instance_name (

// .CLK(CLK), // input wire CLK

// .A(A), // input wire [9 : 0] A

// .B(B), // input wire [9 : 0] B

// .SCLR(SCLR), // input wire SCLR

// .P(P) // output wire [19 : 0] P

//);

//================================================

wire[21:0]y1;

wire[21:0]cr1;

wire[21:0]cb1;

//================================================

wire[19:0]yr;

wire[19:0]yg;

wire[19:0]yb;

mult mult_yr(

.CLK (clk),

.A (10'd306),

.B ({r,2'b00}),

.SCLR (ena),

.P (yr)

);

mult mult_yg(

.CLK (clk),

.A (10'd601),

.B ({g,2'b00}),

.SCLR (ena),

.P (yg)

);

mult mult_yb(

.CLK (clk),

.A (10'd116),

.B ({b,2'b00}),

.SCLR (ena),

.P (yb)

);

assign y1 = yr + yg + yb;

assign y = y1[21:14];//y计算公式

wire[19:0]crr;

wire[19:0]crg;

wire[19:0]crb;

mult mult_crr(

.CLK (clk),

.A (10'd512),

.B ({r,2'b00}),

.SCLR (ena),

.P (crr)

);

mult mult_crg(

.CLK (clk),

.A (10'd429),

.B ({g,2'b00}),

.SCLR (ena),

.P (crg)

);

mult mult_crb(

.CLK (clk),

.A (10'd83),

.B ({b,2'b00}),

.SCLR (ena),

.P (crb)

);

assign cr1 = crr - crg - crb;

assign cr = cr1[21:14]+128;//cr计算公式

wire[19:0]cbr;

wire[19:0]cbg;

wire[19:0]cbb;

mult mult_cbr(

.CLK (clk),

.A (10'd173),

.B ({r,2'b00}),

.SCLR (ena),

.P (cbr)

);

mult mult_cbg(

.CLK (clk),

.A (10'd339),

.B ({g,2'b00}),

.SCLR (ena),

.P (cbg)

);

mult mult_cbb(

.CLK (clk),

.A (10'd512),

.B ({b,2'b00}),

.SCLR (ena),

.P (cbb)

);

assign cb1 = cbb - cbr - cbg;

assign cb = cb1[21:14]+128;//cb计算公式

endmodule

09_045_m