1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/Y56cmZZs

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

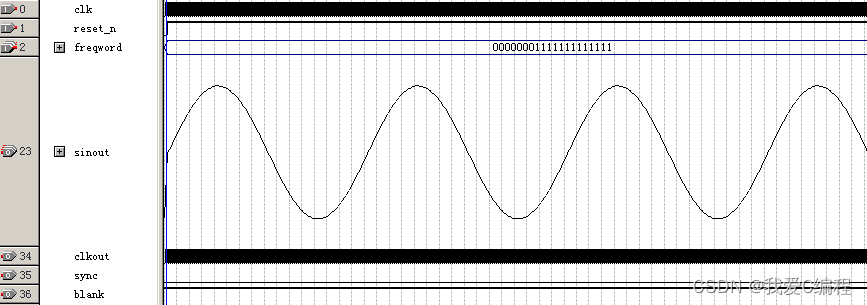

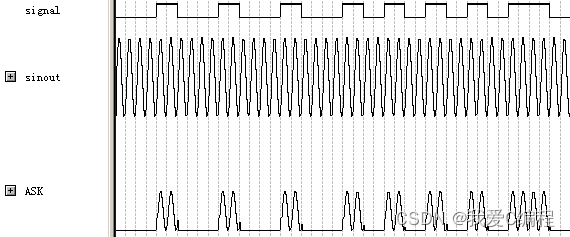

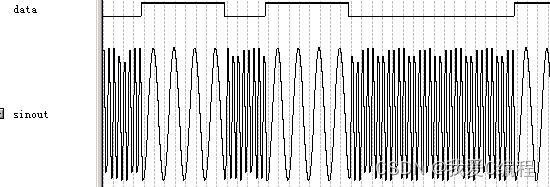

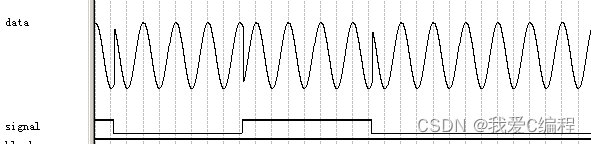

2.部分仿真图预览

3.算法概述

直接数字频率合成技术 (Direct Digital Synthesis)完全不同于我们己经熟悉的直接频率合成技术和锁相环频率合成技术。直接数字频率合成技术(简称DDS)的理论早在七十年代就被提出。它的基本原理就是利用采样定理,通过查表法产生波形,由于硬件技术的限制,DDS技术当时没能得到广泛应用。随着大规模集成电路技术的飞速发展,DDS技术的优越性己逐步显现出来。不少学者认为,DDS是产生信号和频率的一种理想方法,发展前景十分广阔。与其他频率合成方法相比较,直接数字频率合成技术的主要优点是易于程控,相位连续,输出频率稳定度高,分辨率高。其频率分辨率可以达到10-3。而且频率转换速度快,可小于100ns,特别适宜用在跳频无线通信系统。其相位噪声主要决定于参考时钟振荡器。

DDS(Direct Digital frequency Synthesis)即直接数字频率合成器,是一种新型的频率合成技术,具有较高的频率分辨率,快速的频率切换,稳定性好,可灵活产生多种信号的优点。因此,在现代电子系统及设备的频率源设计中,尤其在通信领域,直接数字频率合成器的应用越来越广泛。在数字化的调制解调模块中。DDS取代了VCO(模拟的压控振荡器),被大量应用。这种合成技术是一种利用数字技术来控制信号的相位增量的技术,它采用插值取样的方式,将要合成的正弦波波形用若干个采样点的取值来代替,然后依次等时间间隔输出这些取值,每个采样点的值由预先存储的数字值经D/A转换后得到。

4.部分源码

module DDS(clk,reset_n,freqword,sync,blank,sinout,clkout);

input clk;

input reset_n;

input [19:0] freqword;//频率控制字改变值改变频率

output [9:0] sinout;//数据输出

output sync,blank,clkout;

reg [9:0] sinout;

reg [19:0] add;

wire [9:0] addr;

wire [9:0] data;

assign sync=0;

assign blank=1;

assign clkout=clk;

always@(posedge clk or negedge reset_n)

begin

if(~reset_n)

sinout<=10'd0;

else

sinout<=data;

end

always@(posedge clk )

begin

if(~reset_n)

add<=20'd0;

else

add<=add+freqword;

end

assign addr=add[19:10];

rom0 rom0_instant(

.ad(addr),

.q(data)

);

endmodule

/***************************************************************/

module rom0(ad,q);

input [9:0] ad;

output [9:0] q;

reg[9:0] q;

always @(ad)

begin

case(ad)

0:q=10'h200;1:q=10'h203;2:q=10'h206;3:q=10'h209;4:q=10'h20c; 5:q=10'h20f;

6:q=10'h212;7:q=10'h215;8:q=10'h219;9:q=10'h21c;10:q=10'h21f;11:q=10'h222;

12:q=10'h225;13:q=10'h228;14:q=10'h22b;15:q=10'h22f;16:q=10'h232;17:q=10'h235;

...................................................................

default:q=10'h200;

endcase

end

endmodule

A349