1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZZWZlZxv

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

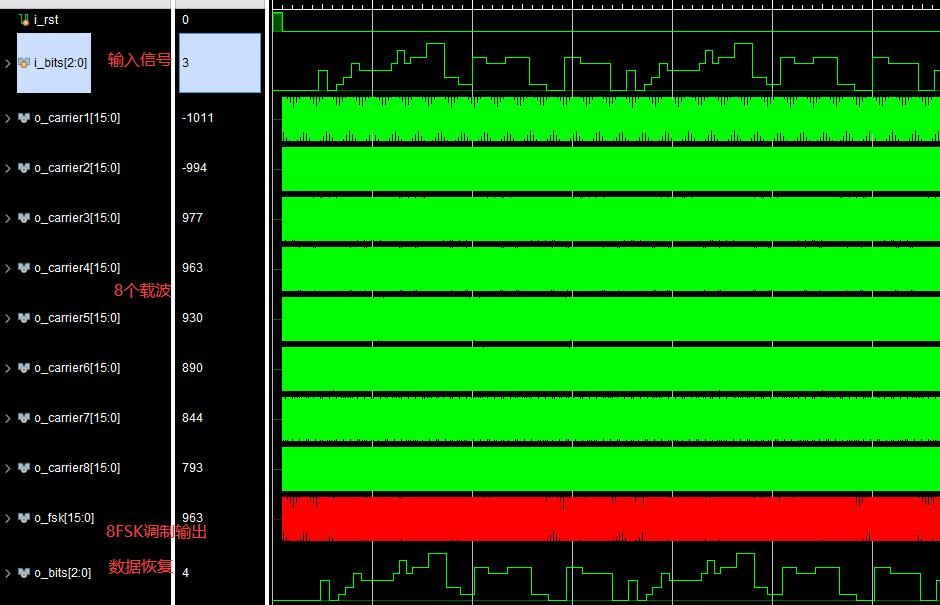

2.部分仿真图预览

3.算法概述

8FSK(8-Frequency Shift Keying)是一种常用的数字调制方法,它通过在不同的频率上发送二进制数据来进行通信。8FSK在通信系统中被广泛应用,因为它具有较高的数据传输速率和较强的抗干扰能力。在8FSK中,每个二进制位被发送在一个特定的频率上。发送频率根据发送的数据位而变化,具体地说,发送的频率根据发送的二进制位的值确定。具体地,8FSK使用8个不同的频率来表示8个不同的二进制位。频率f0到f7对应于二进制位000到111。每个频率对应于一个特定的时间间隔,称为符号时间。

4.部分源码

`timescale 1ns / 1ps

//

//

module test_FSK;

reg i_clk;

reg i_rst;

reg[2:0]i_bits;

wire signed[15:0]o_carrier1;

wire signed[15:0]o_carrier2;

wire signed[15:0]o_carrier3;

wire signed[15:0]o_carrier4;

wire signed[15:0]o_carrier5;

wire signed[15:0]o_carrier6;

wire signed[15:0]o_carrier7;

wire signed[15:0]o_carrier8;

wire signed[31:0]o_de_fsk1;

wire signed[31:0]o_de_fsk2;

wire signed[31:0]o_de_fsk3;

wire signed[31:0]o_de_fsk4;

wire signed[31:0]o_de_fsk5;

wire signed[31:0]o_de_fsk6;

wire signed[31:0]o_de_fsk7;

wire signed[31:0]o_de_fsk8;

wire signed[15:0]o_fsk;

wire [2:0]o_bits;

FSK uut(

.i_clk(i_clk),

.i_rst(i_rst),

.i_bits(i_bits),

.o_carrier1(o_carrier1),

.o_carrier2(o_carrier2),

.o_carrier3(o_carrier3),

.o_carrier4(o_carrier4),

.o_carrier5(o_carrier5),

.o_carrier6(o_carrier6),

.o_carrier7(o_carrier7),

.o_carrier8(o_carrier8),

.o_fsk(o_fsk),

.o_de_fsk1(o_de_fsk1),

.o_de_fsk2(o_de_fsk2),

.o_de_fsk3(o_de_fsk3),

.o_de_fsk4(o_de_fsk4),

.o_de_fsk5(o_de_fsk5),

.o_de_fsk6(o_de_fsk6),

.o_de_fsk7(o_de_fsk7),

.o_de_fsk8(o_de_fsk8),

.o_bits(o_bits)

);

initial

begin

i_clk = 1'b1;

i_rst = 1'b1;

#1000

i_rst = 1'b0;

end

initial

begin

i_bits= 3'b000;

#3050

repeat(100)

begin

#700

i_bits= 3'b000;

#900

i_bits= 3'b011;

#880

i_bits= 3'b000;

#900

i_bits= 3'b001;

#700

i_bits= 3'b010;

#800

i_bits= 3'b100;

#800

i_bits= 3'b011;

#1600

i_bits= 3'b011;

#1600

i_bits= 3'b100;

#600

i_bits= 3'b110;

#700

i_bits= 3'b100;

#600

i_bits= 3'b101;

#1600

i_bits= 3'b111;

#1800

i_bits= 3'b010;

#1400

i_bits= 3'b01;

#1400

i_bits= 3'b101;

#1400

i_bits= 3'b100;

#1900

i_bits= 3'b101;

#1700

i_bits= 3'b101;

#700

i_bits= 3'b001;

#1700

i_bits= 3'b000;

#1800

i_bits= 3'b101;

#1600

i_bits= 3'b100;

#1400

i_bits= 3'b100;

#1600

i_bits= 3'b000;

end

end

always #5 i_clk=~i_clk;

endmodule

00_048m

---