1.完整项目描述和程序获取

>面包多安全交易平台:

QII:https://mbd.pub/o/bread/ZJqZkpps

Vivado:https://mbd.pub/o/bread/ZJqZkppt

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

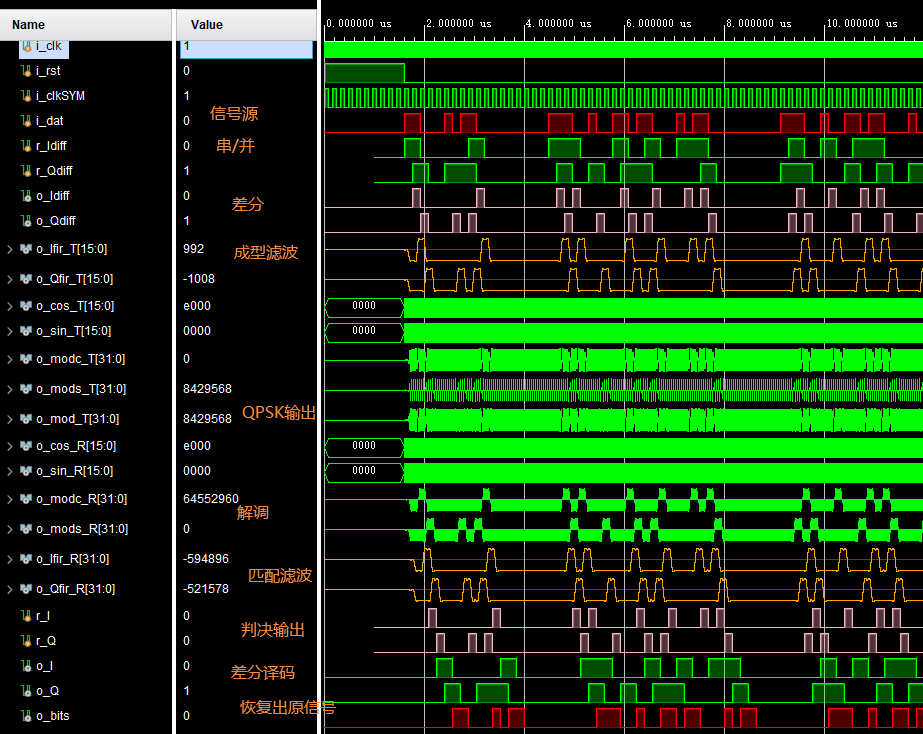

2.部分仿真图预览

3.算法概述

DQPSK调制解调通信系统是一种数字通信系统,用于将数字信息转换为电信号进行传输。DQPSK代表差分四相移键控调制,是一种数字调制技术,它在发送端对数字信息进行编码,并在接收端对信号进行解码。DQPSK调制解调通信系统具有高效、可靠和抗干扰等优点,在现代通信系统中得到广泛应用。

4.部分源码

module TEST();

reg i_clk;

reg i_rst;

reg i_clkSYM;

reg i_dat;

wire o_Idiff;

wire o_Qdiff;

wire signed[15:0]o_Ifir_T;

wire signed[15:0]o_Qfir_T;

wire signed[15:0]o_cos_T;

wire signed[15:0]o_sin_T;

wire signed[31:0]o_modc_T;

wire signed[31:0]o_mods_T;

wire signed[31:0]o_mod_T;

wire signed[15:0]o_cos_R;

wire signed[15:0]o_sin_R;

wire signed[31:0]o_modc_R;

wire signed[31:0]o_mods_R;

wire signed[31:0]o_Ifir_R;

wire signed[31:0]o_Qfir_R;

wire o_I;

wire o_Q;

wire o_bits;

//DQPSK调制

TDQPSK TQPSKU(

.i_clk (i_clk),

.i_rst (i_rst),

.i_clkSYM(i_clkSYM),

.i_dat (i_dat),

.o_Idiff(o_Idiff),

.o_Qdiff(o_Qdiff),

.o_Ifir (o_Ifir_T),

.o_Qfir (o_Qfir_T),

.o_cos (o_cos_T),

.o_sin (o_sin_T),

.o_modc (o_modc_T),

.o_mods (o_mods_T),

.o_mod (o_mod_T)

);

//DQPSK解调

RDQPSK RQPSKU(

.i_clk (i_clk),

.i_rst (i_rst),

.i_clkSYM(i_clkSYM),

.i_med (o_mod_T[25:10]),

.o_cos (o_cos_R),

.o_sin (o_sin_R),

.o_modc (o_modc_R),

.o_mods (o_mods_R),

.o_Ifir (o_Ifir_R),

.o_Qfir (o_Qfir_R),

.o_I(o_I),

.o_Q(o_Q),

.o_bits(o_bits)

);

initial

begin

i_clk = 1'b1;

i_clkSYM=1'b1;

i_rst = 1'b1;

#1600

i_rst = 1'b0;

end

always #5 i_clk=~i_clk;

always #80 i_clkSYM=~i_clkSYM;

initial

begin

i_dat = 1'b0;

#1440

repeat(10)

begin

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

end

$stop();

end

endmodule

00_016m