1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZpeTmJZx

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

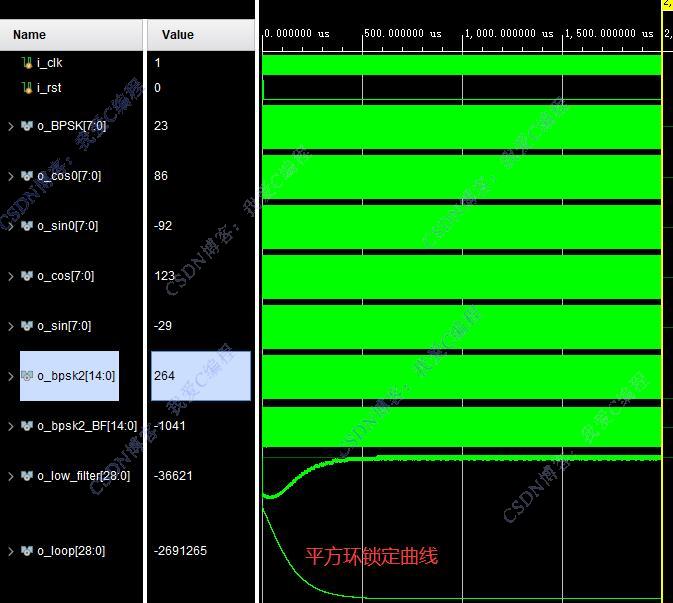

2.部分仿真图预览

3.算法概述

平方环是一种常用的相干解调方法。调制信号经过一个平方装置,进行平方操作,再经过一个中心频率为2fc的带通滤波器,滤除直流成分和携带的部分信息成分,得到二倍频信号cos(4πfct+2φ)。使用倍频信号驱动锁相环,得到对应的正弦信号sin(4πfct+2φ),经过二分频和90°相移,获得载波信号,从而用于相干解调获得基带信号s(t)。

4.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/06/13 06:03:25

// Design Name:

// Module Name: tops_squarePLL

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tops_squarePLL(

input i_clk, //时钟

input i_rst, //复位信号

input signed[1:0]i_X, //输入数据:32MHz

output signed[7:0]o_BPSK,

output signed[7:0]o_cos0,

output signed[7:0]o_sin0,

output signed[7:0]o_cos,

output signed[7:0]o_sin,

output signed[14:0]o_bpsk2,

output signed[14:0]o_bpsk2_BF,

output signed[28:0]o_low_filter,

output signed[28:0]o_loop

);

bpsk_MOD bpsk_MOD_u(

.i_clk (i_clk), //时钟

.i_rst (i_rst), //复位信号

.i_X (i_X), //输入数据:32MHz

.o_BPSK (o_BPSK),

.o_cos (o_cos0),

.o_sin (o_sin0)

);

tops tops_u(

.i_clk (i_clk), //时钟

.i_rst (i_rst), //复位信号

.i_bpsk (o_BPSK), //输入数据:32MHz

.o_cos (o_cos),

.o_sin (o_sin),

.o_bpsk2 (o_bpsk2),

.o_bpsk2_BF (o_bpsk2_BF),

.o_sinXcos (),

.o_BFsinXcos (),

.o_low_filter (o_low_filter),

.o_loop (o_loop)

);

endmodule

00_066m

---