1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/mbd-ZJyUmppv

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

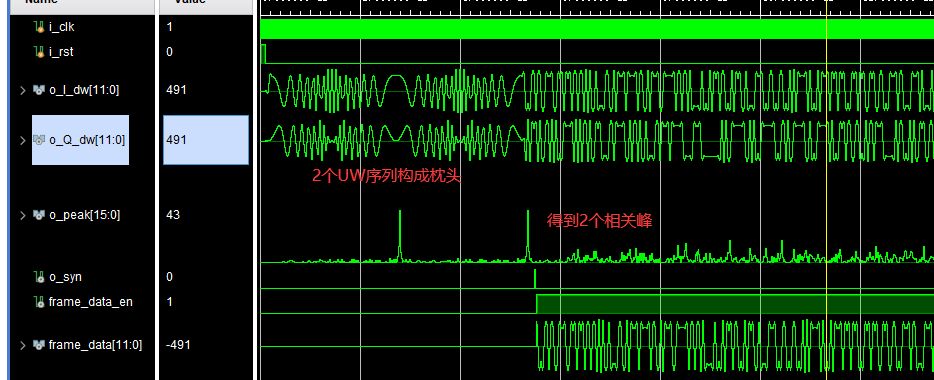

2.部分仿真图预览

3.算法概述

在通信系统中,发送端将数据划分为多个数据帧,并在每个数据帧的开始位置插入同步序列,以便接收端正确识别数据帧的边界。数据帧检测的目标是在接收到的信号中找到同步序列,从而确定数据帧的起始位置。双UW序列作为一种特殊的同步序列,可以通过在接收端进行相关运算来实现数据帧检测。

4.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/07/24 21:40:51

// Design Name:

// Module Name: TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST();

// Inputs

reg i_clk;

reg i_rst;

// Outputs

wire [11:0] o_I_dw;

wire [11:0] o_Q_dw;

wire[15:0] o_peak;

wire o_syn;

wire frame_data_en;

wire [11:0] frame_data;

// Instantiate the Unit Under Test (UUT)

UW_2_sycn uut (

.i_clk (i_clk),

.i_rst (i_rst),

.o_I_dw (o_I_dw),

.o_Q_dw (o_Q_dw),

.o_peak (o_peak),

.o_syn (o_syn),

.frame_data_en(frame_data_en),

.frame_data (frame_data)

);

initial begin

// Initialize Inputs

i_clk = 1;

i_rst = 1;

// Wait 100 ns for global reset to finish

#100

i_rst = 0;

// Add stimulus here

end

always #5 i_clk=~i_clk;

endmodule

00_032m