1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZZWUkp1u

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

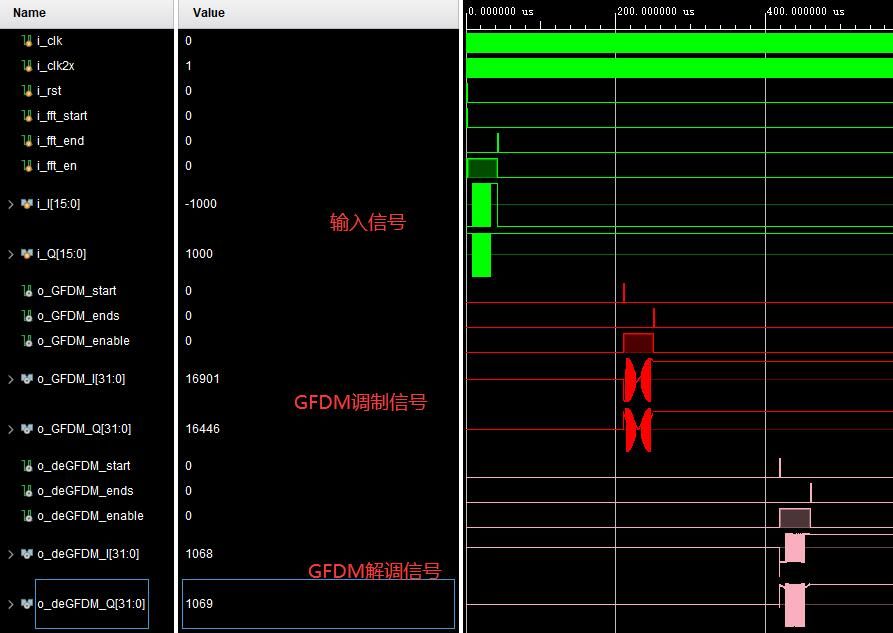

2.部分仿真图预览

3.算法概述

随着通信技术的不断发展,人们对数据传输速率和频谱效率的要求越来越高。为了满足这些需求,一种名为广义频分复用(GFDM)的新型调制技术应运而生。GFDM具有灵活的子载波间隔和符号时间长度,能够在各种复杂环境中实现高效的数据传输。

GFDM是一种基于子载波的多载波调制技术,通过对子载波进行调制和解调来实现数据传输。与传统的正交频分复用(OFDM)相比,GFDM具有更灵活的子载波间隔和符号时间长度,可以更好地适应不同的信道环境。

4.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST_GFDM;

reg i_clk;

reg i_clk2x;

reg i_rst;

reg i_fft_start;

reg i_fft_end;

reg i_fft_en;

reg signed[15:0]i_I;

reg signed[15:0]i_Q;

wire o_GFDM_start;

wire o_GFDM_ends ;

wire o_GFDM_enable;

wire signed[31:0]o_GFDM_I;

wire signed[31:0]o_GFDM_Q;

wire o_deGFDM_start;

wire o_deGFDM_ends ;

wire o_deGFDM_enable;

wire signed[31:0]o_deGFDM_I;

wire signed[31:0]o_deGFDM_Q;

GFDM GFDM_u(

.i_clk (i_clk),

.i_clk2x (i_clk2x),

.i_rst (i_rst),

.i_fft_start (i_fft_start),

.i_fft_end (i_fft_end),

.i_fft_en (i_fft_en),

.i_I (i_I),

.i_Q (i_Q),

.o_GFDM_start (o_GFDM_start),

.o_GFDM_ends (o_GFDM_ends),

.o_GFDM_enable (o_GFDM_enable),

.o_GFDM_I (o_GFDM_I),

.o_GFDM_Q (o_GFDM_Q),

.o_deGFDM_start (o_deGFDM_start),

.o_deGFDM_ends (o_deGFDM_ends),

.o_deGFDM_enable (o_deGFDM_enable),

.o_deGFDM_I (o_deGFDM_I),

.o_deGFDM_Q (o_deGFDM_Q)

);

reg [15:0]cnts;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

cnts <= 16'd0;

i_I <= -1000;

i_Q <= 1000;

end

else begin

if(i_fft_en == 1'b1)

begin

cnts <= cnts+16'd1;

if(cnts>=16'd400 & cnts<=16'd1648)

begin

i_I <= ~i_I;

if (cnts[0]==1'b1)

i_Q <= ~i_Q;

else

i_Q <= i_Q;

end

end

else begin

cnts <= 16'd0;

i_I <= -1000;

i_Q <= 1000;

end

end

end

reg [19:0]cnts2;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

cnts2 <= 20'd0;

i_fft_start<=1'b0;

i_fft_en <=1'b0;

i_fft_end <=1'b0;

end

else begin

if(cnts2==20'd30000)

cnts2 <= 20'd0;

else

cnts2 <= cnts2 + 20'd1;

if(cnts2==20'd0)

begin

i_fft_start<=1'b1;

i_fft_en <=1'b0;

i_fft_end <=1'b0;

end

if(cnts2==20'd1)

begin

i_fft_start<=1'b1;

i_fft_en <=1'b0;

i_fft_end <=1'b0;

end

if(cnts2==20'd2)

begin

i_fft_start<=1'b1;

i_fft_en <=1'b0;

i_fft_end <=1'b0;

end

if(cnts2==20'd3)

begin

i_fft_start<=1'b1;

i_fft_en <=1'b0;

i_fft_end <=1'b0;

end

if(cnts2==20'd4)

begin

i_fft_start<=1'b0;

i_fft_en <=1'b0;

i_fft_end <=1'b0;

end

if(cnts2>=20'd5 & cnts2<=20'd4+2047)

begin

i_fft_start<=1'b0;

i_fft_en <=1'b1;

i_fft_end <=1'b0;

end

if(cnts2==20'd4+2048)

begin

i_fft_start<=1'b0;

i_fft_en <=1'b1;

i_fft_end <=1'b1;

end

if(cnts2>20'd4+2048)

begin

i_fft_start<=1'b0;

i_fft_en <=1'b0;

i_fft_end <=1'b0;

end

end

end

initial

begin

i_clk2x= 1'b1;

i_clk = 1'b1;

i_rst = 1'b1;

#1000

i_rst = 1'b0;

end

always #10 i_clk=~i_clk;

always #5 i_clk2x=~i_clk2x;

endmodule

00_045m