1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJ2WmZdx

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

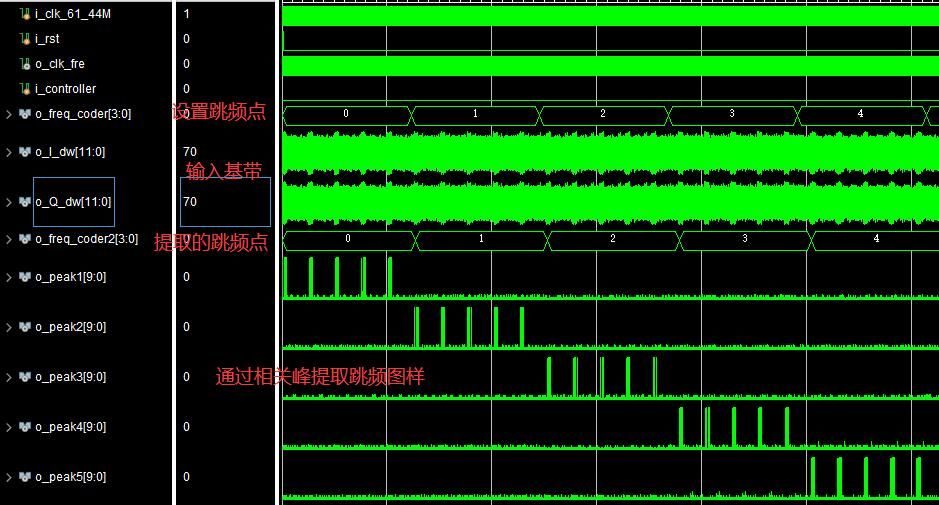

2.部分仿真图预览

3.算法概述

插入导频: 跳频信号在传输过程中可能会经历频率变化,这使得信号的频谱随时间变化。为了帮助识别信号的频率,我们在跳频信号中插入导频序列。导频序列是预先知道的、不随时间变化的信号,它可以用来估计信号的频率偏移。

相关峰判决法: 跳频图样识别基于导频序列的相关峰。在收到信号后,首先通过相关操作计算信号与导频序列之间的相关性。当信号的频率与导频序列的频率相匹配时,相关性峰值最高。通过检测相关性峰值,我们可以判断信号是否匹配特定的跳频图样。

4.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/04/22 15:13:09

// Design Name:

// Module Name: tops

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tops(

i_clk_61_44M,//输入时钟

i_rst, //复位

o_clk_fre,

i_controller,

o_freq_coder,

o_I_dw,

o_Q_dw,

o_freq_coder2,

o_peak1,

o_peak2,

o_peak3,

o_peak4,

o_peak5

);

input i_clk_61_44M;

input i_rst;

output o_clk_fre;

input i_controller;

output[3:0]o_freq_coder;

output signed[11:0]o_I_dw;

output signed[11:0]o_Q_dw;

output[3:0] o_freq_coder2;

output signed[9:0]o_peak1;

output signed[9:0]o_peak2;

output signed[9:0]o_peak3;

output signed[9:0]o_peak4;

output signed[9:0]o_peak5;

wire clk_61_44M;

wire clk_15_36M;

wire clk_7_68M;

clk_wiz_0 clk_wiz_0_u

(

// Clock out ports

.clk_out1(clk_61_44M), // output clk_out1

.clk_out2(clk_15_36M), // output clk_out2

.clk_out3(clk_7_68M), // output clk_out3

// Status and control signals

.reset (1'b0), // input reset

.locked (), // output locked

// Clock in ports

.clk_in1 (i_clk_61_44M)

);

assign o_clk_fre=clk_15_36M;

wire signed[11:0]w_I_dw1;

wire signed[11:0]w_Q_dw1;

wire signed[11:0]w_I_dw2;

wire signed[11:0]w_Q_dw2;

wire signed[11:0]w_I_dw3;

wire signed[11:0]w_Q_dw3;

wire signed[11:0]w_I_dw4;

wire signed[11:0]w_Q_dw4;

wire signed[11:0]w_I_dw5;

wire signed[11:0]w_Q_dw5;

signal_f1 signal_f1_u(

.i_clk (o_clk_fre),

.i_rst (i_rst),

.o_I_dw(w_I_dw1),

.o_Q_dw(w_Q_dw1)

);

signal_f2 signal_f2_u(

.i_clk (o_clk_fre),

.i_rst (i_rst),

.o_I_dw(w_I_dw2),

.o_Q_dw(w_Q_dw2)

);

signal_f3 signal_f3_u(

.i_clk (o_clk_fre),

.i_rst (i_rst),

.o_I_dw(w_I_dw3),

.o_Q_dw(w_Q_dw3)

);

signal_f4 signal_f4_u(

.i_clk (o_clk_fre),

.i_rst (i_rst),

.o_I_dw(w_I_dw4),

.o_Q_dw(w_Q_dw4)

);

signal_f5 signal_f5_u(

.i_clk (o_clk_fre),

.i_rst (i_rst),

.o_I_dw(w_I_dw5),

.o_Q_dw(w_Q_dw5)

);

jump_frequency jump_frequency_u(

.i_clk (o_clk_fre),

.i_rst (i_rst),

.i_controller (i_controller),

.i_freqset (4'b0010),

.o_freq_coder (o_freq_coder)//输出跳频带你

);

reg signed[11:0]o_I_dw;

reg signed[11:0]o_Q_dw;

always @(posedge o_clk_fre or posedge i_rst)

begin

if(i_rst)

begin

o_I_dw <= 12'd0;

o_Q_dw <= 12'd0;

end

else begin

if(o_freq_coder == 4'b0000)//根据不同的频点,插入不同的序列,接收端根据序列类型判决频点

begin

o_I_dw <= w_I_dw1;

o_Q_dw <= w_I_dw1;

end

if(o_freq_coder == 4'b0001)

begin

o_I_dw <= w_I_dw2;

o_Q_dw <= w_I_dw2;

end

if(o_freq_coder == 4'b0010)

begin

o_I_dw <= w_I_dw3;

o_Q_dw <= w_I_dw3;

end

if(o_freq_coder == 4'b0011)

begin

o_I_dw <= w_I_dw4;

o_Q_dw <= w_I_dw4;

end

if(o_freq_coder == 4'b0100)

begin

o_I_dw <= w_I_dw5;

o_Q_dw <= w_I_dw5;

end

end

end

jump_check jump_check_u(

.i_clk (o_clk_fre),

.i_rst (i_rst),

.i_I_dw (o_I_dw),

.i_Q_dw (o_Q_dw),

.o_freq_coder(o_freq_coder2),

.o_peak1 (o_peak1),

.o_peak2 (o_peak2),

.o_peak3 (o_peak3),

.o_peak4 (o_peak4),

.o_peak5 (o_peak5)

);

endmodule

00_040m