1.完整项目描述和程序获取

>面包多安全交易平台:

QII:https://mbd.pub/o/bread/ZJuXmpts

vivado:https://mbd.pub/o/bread/ZJuXmptw

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

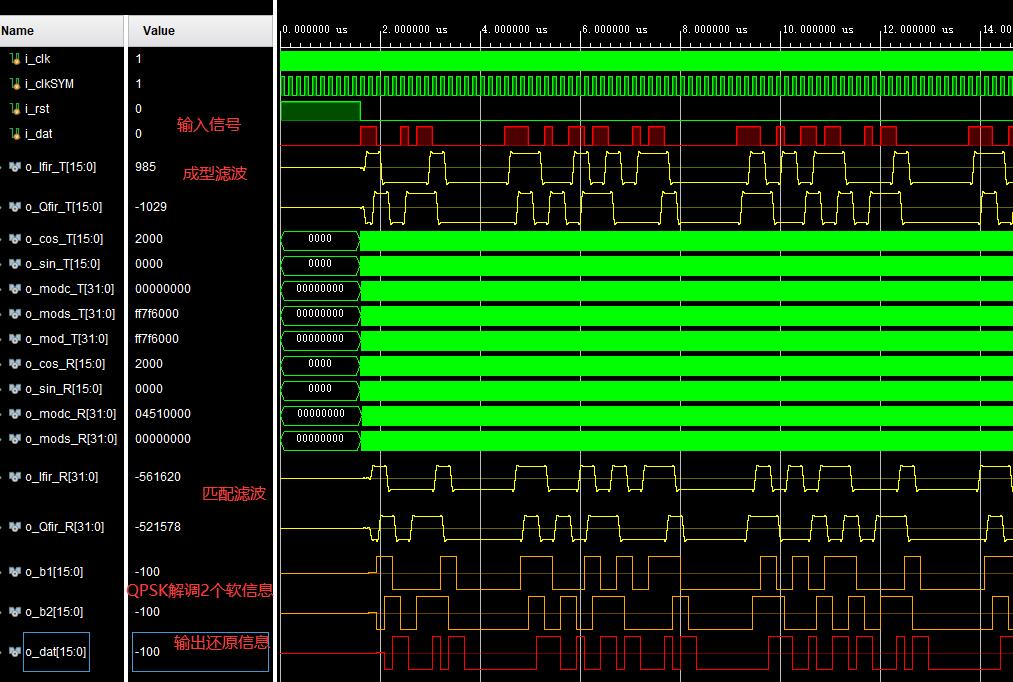

2.部分仿真图预览

3.算法概述

QPSK是一种常用的调制方式,通过将两个比特映射到一个复平面上的相位点,实现了高效的信号传输。软解调是一种基于接收信号的概率估计进行解调的方法,能够提供更好的性能。本文将逐步介绍QPSK软解调的实现过程,包括信号采样、相位估计、判决和解调等方面。软解调是一种通过概率估计实现解调的方法,能够在信道噪声存在的情况下提供更好的性能。QPSK是一种常用的调制方式,通过将两个比特映射到相位点,实现了高效的信号传输。

4.部分源码

`timescale 1ns / 1ps

module TEST();

reg i_clk;

reg i_clkSYM;

reg i_rst;

reg i_dat;

wire signed[15:0]o_Ifir_T;

wire signed[15:0]o_Qfir_T;

wire signed[15:0]o_cos_T;

wire signed[15:0]o_sin_T;

wire signed[31:0]o_modc_T;

wire signed[31:0]o_mods_T;

wire signed[31:0]o_mod_T;

wire signed[15:0]o_cos_R;

wire signed[15:0]o_sin_R;

wire signed[31:0]o_modc_R;

wire signed[31:0]o_mods_R;

wire signed[31:0]o_Ifir_R;

wire signed[31:0]o_Qfir_R;

wire signed[15:0]o_b1;

wire signed[15:0]o_b2;

wire signed[15:0]o_dat;

//QPSK调制

TQPSK TQPSKU(

.i_clk (i_clk),

.i_clkSYM(i_clkSYM),

.i_rst (i_rst),

.i_dat(i_dat),

.o_Ifir (o_Ifir_T),

.o_Qfir (o_Qfir_T),

.o_cos (o_cos_T),

.o_sin (o_sin_T),

.o_modc (o_modc_T),

.o_mods (o_mods_T),

.o_mod (o_mod_T)

);

//QPSK解调

RQPSK RQPSKU(

.i_clk (i_clk),

.i_rst (i_rst),

.i_clkSYM(i_clkSYM),

.i_med (o_mod_T[25:10]),

.o_cos (o_cos_R),

.o_sin (o_sin_R),

.o_modc (o_modc_R),

.o_mods (o_mods_R),

.o_Ifir (o_Ifir_R),

.o_Qfir (o_Qfir_R),

.o_b1 (o_b1),

.o_b2 (o_b2),

.o_dat (o_dat)

);

initial

begin

i_clk = 1'b1;

i_clkSYM=1'b1;

i_rst = 1'b1;

#1600

i_rst = 1'b0;

end

always #5 i_clk=~i_clk;

always #80 i_clkSYM=~i_clkSYM;

initial

begin

i_dat = 1'b0;

#1440

repeat(10)

begin

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

end

$stop();

end

//reg[7:0]cmnts;

//always @(posedge i_clk or posedge i_rst)

//begin

// if(i_rst)

// begin

// cmnts <= 8'd0;

// i_Ibits_T<=1'b0;

// i_Qbits_T<=1'b0;

// end

//else begin

// cmnts <= cmnts + 8'd1;

// i_Ibits_T<=cmnts[5];

// i_Qbits_T<=cmnts[6];

// end

//end

endmodule

00_026m