1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJmTkpZq

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

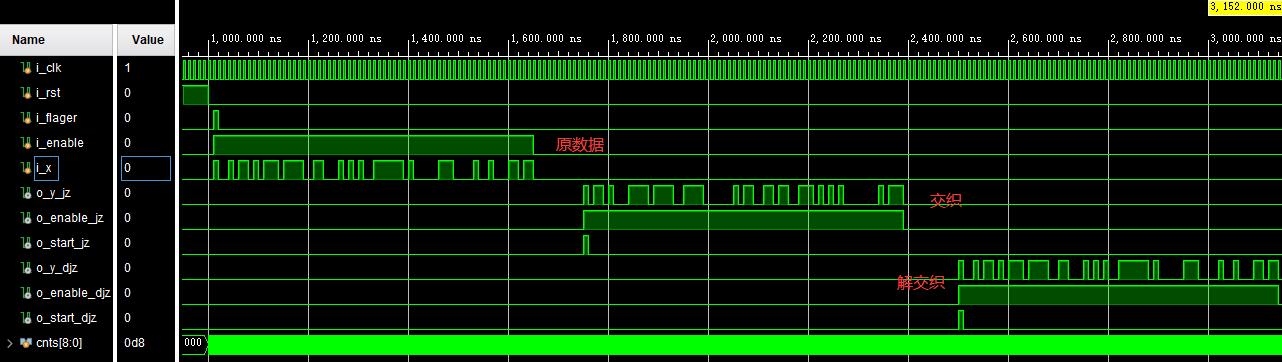

2.部分仿真图预览

3.算法概述

交织解交织系统是一种数据传输技术,广泛应用于通信系统中,以提高数据传输的可靠性和抗干扰能力。该系统通过将数据在发送端进行交织处理,然后在接收端进行解交织处理,使数据的各个位分散到不同的位置上,从而降低信道噪声和干扰的影响,提高数据传输的可靠性。

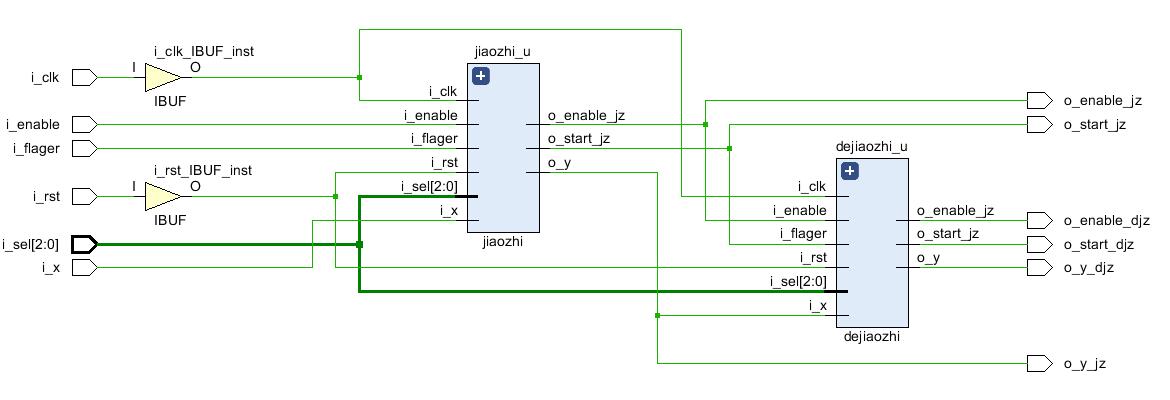

4.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/05/12 19:58:30

// Design Name:

// Module Name: tops

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tops(

input i_clk,

input i_rst,

input [2:0]i_sel,//配置2*2交织和4*4交织

input i_flager,

input i_enable,

input i_x,

output o_y_jz,

output o_enable_jz,

output o_start_jz,

output o_y_djz,

output o_enable_djz,

output o_start_djz

);

//交织

jiaozhi jiaozhi_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_sel (i_sel),//配置2*2交织和4*4交织

.i_flager (i_flager),

.i_enable (i_enable),

.i_x (i_x),

.o_y (o_y_jz),

.o_enable_jz (o_enable_jz),

.o_start_jz (o_start_jz)

);

//解交织

dejiaozhi dejiaozhi_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_sel (i_sel),//配置2*2交织和4*4交织

.i_flager (o_start_jz),

.i_enable (o_enable_jz),

.i_x (o_y_jz),

.o_y (o_y_djz),

.o_enable_jz (o_enable_djz),

.o_start_jz (o_start_djz)

);

endmodule

00_014m