1.������Ŀ�����ͳ����ȡ

>����లȫ����ƽ̨

QUARTUSii:https://mbd.pub/o/bread/ZJialp5p

VIVADO:https://mbd.pub/o/bread/ZJialp5s

>�������ʧЧ������ֱ�Ӵ�վ����������ص��̣�

>�������ʧЧ��������Ա���������Ŀ����Ҳ���Լ��Ż���QQ��ϵ��

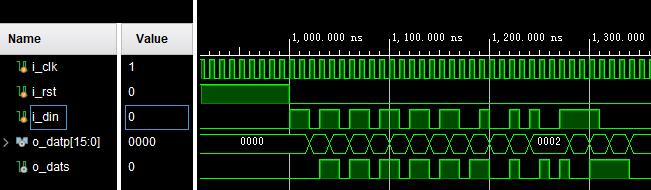

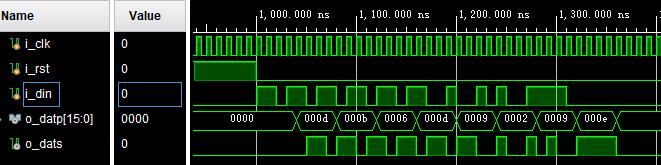

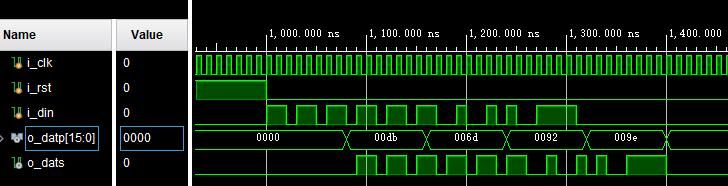

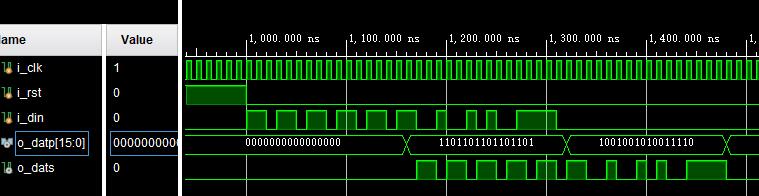

2.���ַ���ͼԤ��

3.�㷨����

����ת���ǽ���������ת��Ϊ�������ݵĹ��̣�����һ�����ݰ�λ��ֳɶ���������ݡ�����ת����������Ϊ���������������Ϊ�������������ڴ���ת�����У���Ҫʹ����λ�Ĵ������洢�������ݣ���ʹ�ö�·ѡ������ѡ������λ��������������������ϡ�

����ת���ǽ���������ת��Ϊ�������ݵĹ��̣���������������ݺϲ���һ�����ݡ�����ת����������Ϊ���������������Ϊ�������������ڲ���ת�����У���Ҫʹ�ö�·ѡ������ѡ������λ����ʹ����λ�Ĵ������洢�������ݣ����䰴λ�ϲ��ɴ������ݡ�

4.����Դ��

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/05/07 19:40:52

// Design Name:

// Module Name: TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST();

reg i_clk;

reg i_rst;

reg i_din;

wire[15:0]o_datp;

wire o_dats;

s2p s2pu1(

.i_clk (i_clk),

.i_rst (i_rst),

.i_sel (2'b00),//00�?·01:4·10�?·11�?6·

.i_din (i_din),

.o_datp (o_datp)

);

p2s p2su2(

.i_clk (i_clk),

.i_rst (i_rst),

.i_sel (2'b00),//00�?·01:4·10�?·11�?6·

.i_din (o_datp),

.o_dats (o_dats)

);

initial

begin

i_clk=1'b1;

i_rst=1'b1;

#1000

i_rst=1'b0;

end

always #5 i_clk=~i_clk;

initial

begin

i_din=1'b0;

#1000

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b0;

#500

$stop();

end

endmodule

00_010m