1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJeclZ5v

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

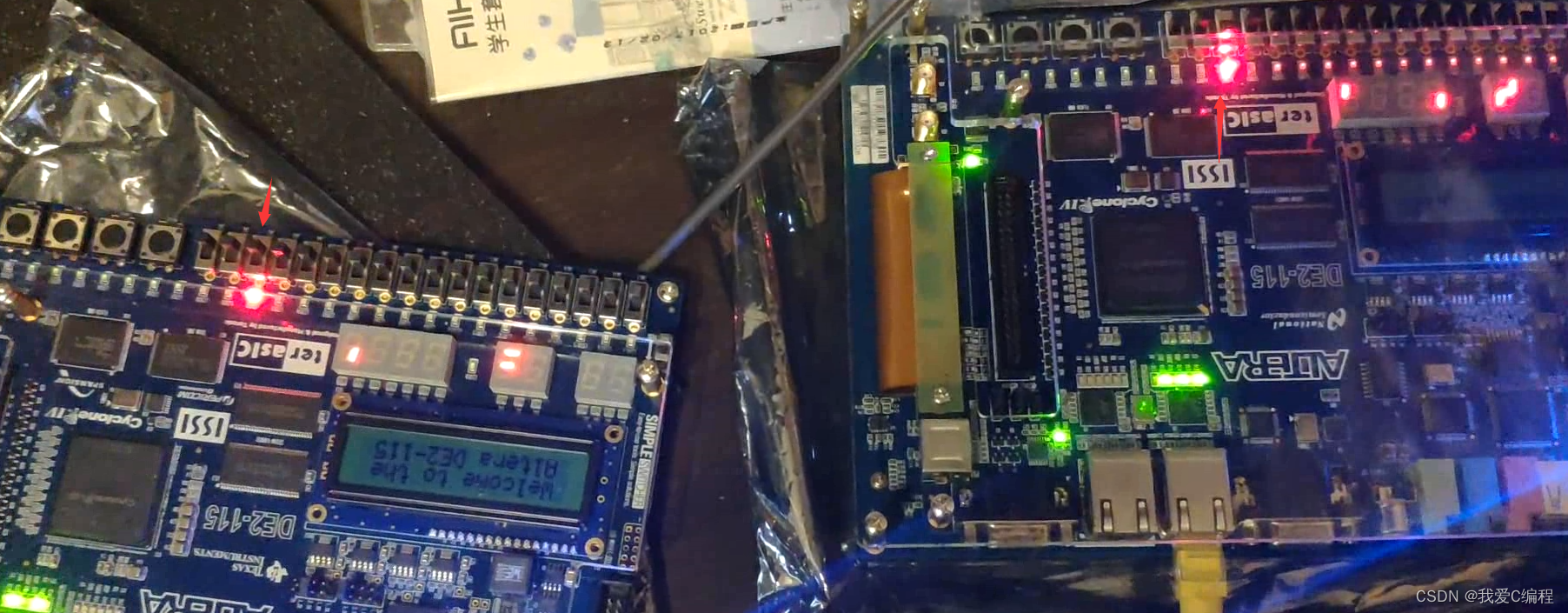

2.部分仿真图预览

3.算法概述

UDP 是User Datagram Protocol的简称, 中文名是用户数据报协议,是OSI(Open System Interconnection,开放式系统互联) 参考模型中一种无连接的传输层协议,提供面向事务的简单不可靠信息传送服务,IETF RFC 768 [1] 是UDP的正式规范。UDP在IP报文的协议号是17。

UDP协议与TCP协议一样用于处理数据包,在OSI模型中,两者都位于传输层,处于IP协议的上一层。UDP有不提供数据包分组、组装和不能对数据包进行排序的缺点,也就是说,当报文发送之后,是无法得知其是否安全完整到达的。UDP用来支持那些需要在计算机之间传输数据的网络应用。包括网络视频会议系统在内的众多的客户/服务器模式的网络应用都需要使用UDP协议。UDP协议从问世至今已经被使用了很多年,虽然其最初的光彩已经被一些类似协议所掩盖,但即使在今天UDP仍然不失为一项非常实用和可行的网络传输层协议。

4.部分源码

reg [15:0] myIP_Prtcl;

reg [159:0]myIP_layer;

reg [63:0] myUDP_layer;

reg [31:0] mydata;

reg [2:0] byte_counter;

reg [4:0] state_counter;

reg [95:0] mymac;

reg [15:0] data_counter;

reg [3:0] rx_state;

wire e_rxdv;

wire[7:0 ]datain;

reg [159:0]IP_layer;

reg [63:0] UDP_layer;

reg [15:0] rx_total_length; //UDP frame的总长度

reg [15:0] rx_data_length; //接收的UDP数据包的长度

reg [31:0] data_o; //UDP接收的数据

assign e_rxdv=1'b1;

assign datain={ENET1_RX_DATA,ENET1_RX_DATA};

parameter idle=4'd0,

six_55=4'd1,

spd_d5=4'd2,

rx_mac=4'd3,

rx_IP_Protocol=4'd4,

rx_IP_layer=4'd5,

rx_UDP_layer=4'd6,

rx_data=4'd7,

rx_finish=4'd8;

initial

begin

rx_state<=idle;

end

//UDP数据接收程序

always@(posedge clk_50)

begin

data_o<={24'd0,datain};

case(rx_state)

idle: begin

byte_counter<=3'd0;

data_counter<=10'd0;

mydata<=32'd0;

state_counter<=5'd0;

if(e_rxdv==1'b1) begin //接收数据有效为高,开始接收数据

if(datain[7:0]==8'h55) begin //接收到第一个55//

rx_state<=six_55;

mydata<={mydata[23:0],datain[7:0]};

end

else

rx_state<=idle;

end

end

six_55: begin //接收6个0x55//

if ((datain[7:0]==8'h55)&&(e_rxdv==1'b1)) begin

if (state_counter==5) begin

state_counter<=0;

rx_state<=spd_d5;

end

else

state_counter<=state_counter+1'b1;

end

else

rx_state<=idle;

end

spd_d5: begin //接收1个0xd5//

if((datain[7:0]==8'hd5)&&(e_rxdv==1'b1))

rx_state<=rx_mac;

else

rx_state<=idle;

end

rx_mac: begin //接收目标mac address和源mac address

if(e_rxdv==1'b1) begin

if(state_counter<5'd11) begin

mymac<={mymac[87:0],datain};

state_counter<=state_counter+1'b1;

end

else begin

state_counter<=5'd0;

if((mymac[87:72]==16'h000a)&&(mymac[71:56]==16'h3501)&&(mymac[55:40]==16'hfec0)) //判断目标MAC Address是否为本FPGA

rx_state<=rx_IP_Protocol;

else

rx_state<=rx_IP_Protocol;

end

end

else

rx_state<=idle;

end

rx_IP_Protocol: begin //接收2个字节的IP TYPE//

if(e_rxdv==1'b1) begin

if(state_counter<5'd1) begin

myIP_Prtcl<={myIP_Prtcl[7:0],datain[7:0]};

state_counter<=state_counter+1'b1;

end

else begin

state_counter<=5'd0;

rx_state<=rx_IP_layer;

end

end

else

rx_state<=idle;

end

rx_IP_layer: begin //接收20字节的udp虚拟包头,ip address

if(e_rxdv==1'b1) begin

if(state_counter<5'd19) begin

myIP_layer<={myIP_layer[151:0],datain[7:0]};

state_counter<=state_counter+1'b1;

end

else begin

IP_layer<={myIP_layer[151:0],datain[7:0]};

state_counter<=5'd0;

rx_state<=rx_UDP_layer;

end

end

else

rx_state<=idle;

end

rx_UDP_layer: begin //接受8字节UDP的端口号及UDP数据包长

rx_total_length<=IP_layer[143:128];

if(e_rxdv==1'b1) begin

if(state_counter<5'd7) begin

myUDP_layer<={myUDP_layer[55:0],datain[7:0]};

state_counter<=state_counter+1'b1;

end

else begin

UDP_layer<={myUDP_layer[55:0],datain[7:0]};

rx_data_length<= myUDP_layer[23:8]; //UDP数据包的长度

state_counter<=5'd0;

rx_state<=rx_data;

end

end

else

rx_state<=idle;

end

rx_data: begin //接收UDP的数据

if(e_rxdv==1'b1) begin

if (data_counter==rx_data_length-9) begin //存最后的数据,真正的UDP数据需要减去8字节的UDP包头

data_counter<=0;

rx_state<=rx_finish;

data_o<={mydata[23:0],datain[7:0]};

byte_counter<=0;

end

else begin

data_counter<=data_counter+1'b1;

if(byte_counter<3'd3) begin

mydata<={mydata[23:0],datain[7:0]};

byte_counter<=byte_counter+1'b1;

end

else begin

data_o<={mydata[23:0],datain[7:0]};

byte_counter<=3'd0;

end

end

end

else

rx_state<=idle;

end

rx_finish: begin

rx_state<=idle;

end

default:rx_state<=idle;

endcase

end

alt_25 alt_25_u(enetclk,MDC);

assign ENET1_MDC=MDC;

assign GTX_CLK=0;

//产生发送的控制使能信号和地址信息

TXcontrol TXcontrol_u(

.TX_CLK(TX_CLK),//网口时钟

.flag (flag),//发送接收周期性标志信号

.addr (ADDR),//地址

.TX_EN (TX_EN),//控制网口的EN信号

.TX_ER (TX_ER)//控制网口的ER信号

);

//寄存器中读取数据或者存放数据

package_wr package_wr_u(

.MDC (MDC),

.flagi (flag),

.mdio_in(mdio_in),

.wr_rd (wr_rd),

.mdio (mdio),

.flag (flag_),

.RST_N (RST_N)

);

12_049_m