核心提示:01_015_m包括程序操作录像...

1.完整项目描述和程序获取

面包多安全交易平台:https://mbd.pub/o/bread/Y5uVmZtp

如果链接失效,程序调试报错或者项目合作可以加微信或者QQ联系。

2.部分源码

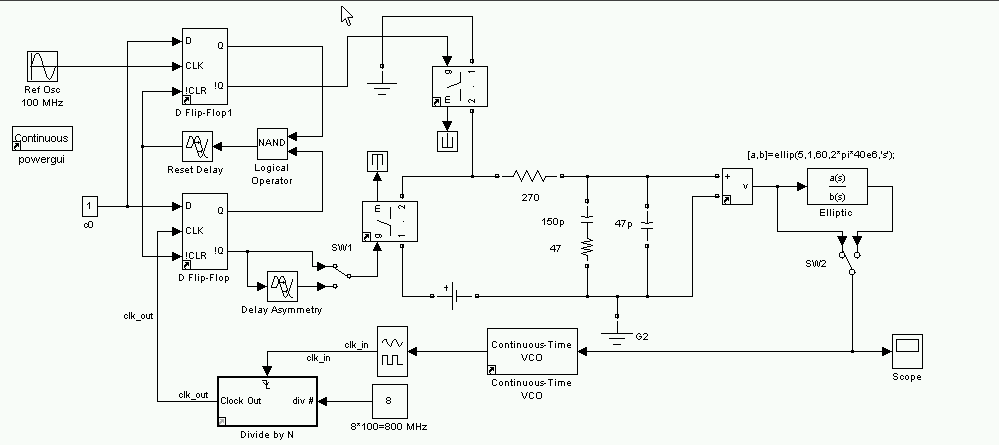

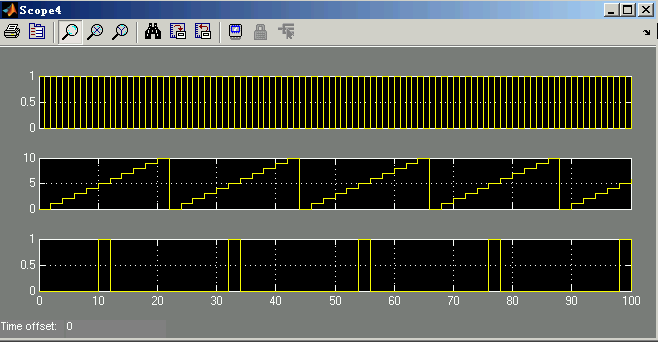

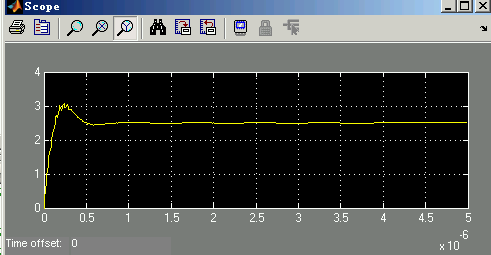

3.部分仿真图预览

4.算法概述

随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副载波同步、图象处理等各个方面得到了广泛的应用。数字锁相环不仅吸收了数字电路可靠性高、体积小、价格低等优点,还解决了模拟锁相环的直流零点漂移、器件饱和及易受电源和环境温度变化等缺点,此外还具有对离散样值的实时处理能力,已成为锁相技术发展的方向。

(1)数字环路鉴相器(DPD)

数字鉴相器也称采样鉴相器,是用来比较输入信号与压控振荡器输出信号的相位,它的输出电压是 对应于这两个信号相位差的函数。它是锁相环路中的关键部件,数字鉴相器的形式可分为:过零采样鉴相器、触发器型数字鉴相器、超前―滞后型数字鉴相器和奈奎斯特速率取样鉴相器。

(2)数字环路滤波器(DLF)

数字环路滤波器在环路中对输入噪声起抑止作用,并且对环路的校正速度起调节作用。数字滤波器是一种专门的技术,有各种各样的结构形式和设计方法。引入数字环路滤波器和模拟锁相环路引入环路滤波器的目的一样,是作为校正网络引入环路的。因此,合理的设计数字环路滤波器和选取合适的数字滤波器结构就能使DPLL满足预定的系统性能要求。

(3) 数字压控振荡器(DCO)

数控振荡器,又称为数字钟。它在数字环路中所处的地位相当于模拟锁相环中的压控振荡器(VCO)。但是,它的输出是一个脉冲序列,而该输出脉冲序列的周期受数字环路滤波器送来的校正信号的控制。其控制特点是:前一采样时刻得到的校正信号将改变下一个采样时刻的脉冲时间位置。