1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/Y5mWlJlt

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

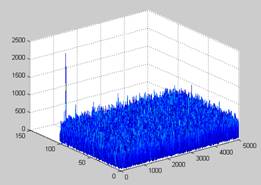

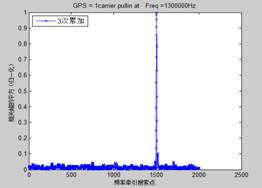

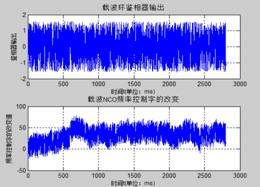

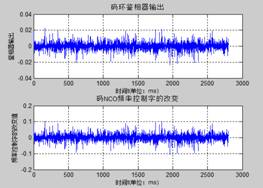

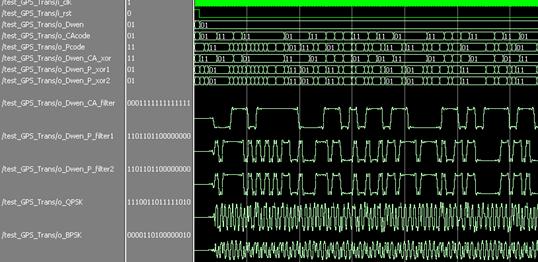

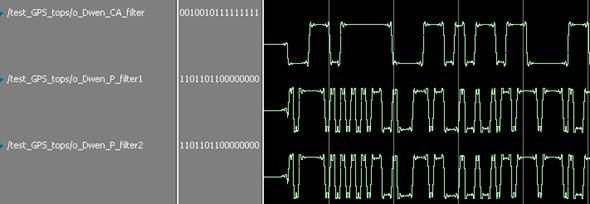

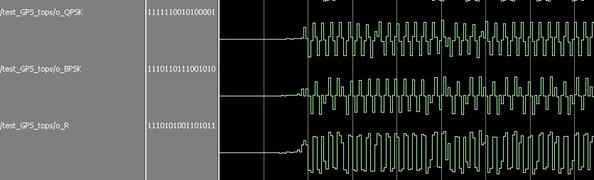

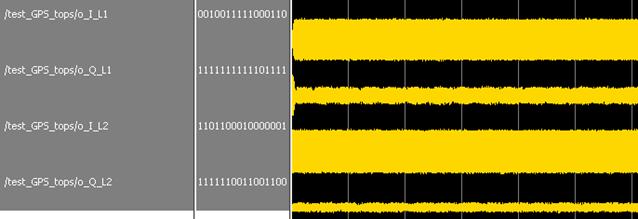

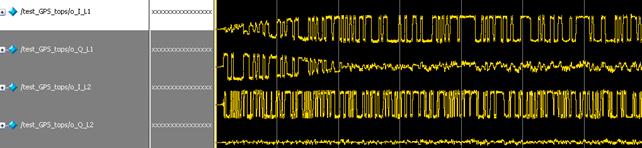

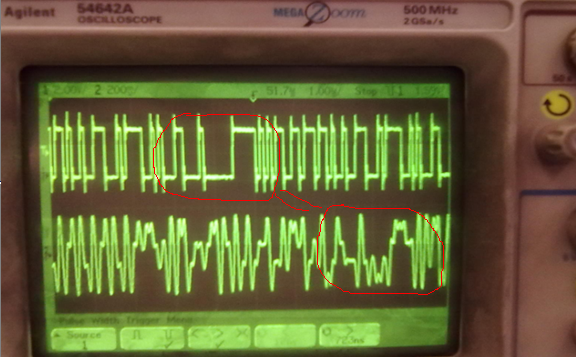

2.部分仿真图预览

3.算法概述

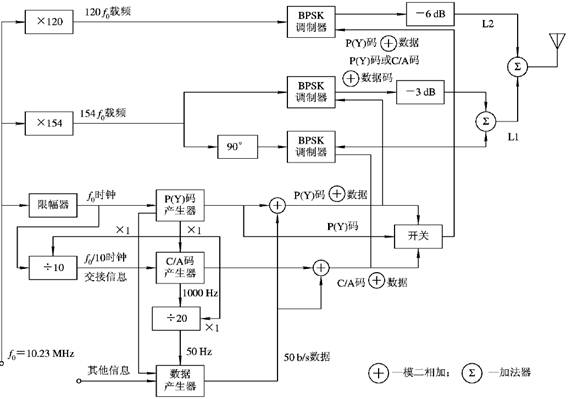

最早的GPS包含L1和L2两个频段,其中L1上调制CA码,P码以及导航电文,L2上调制P码和导航电文。在实际接收到的GPS信号中,我们除了能够接受到CA码和P码外,还能检测到L1和L2两种载波信号。GPS双频发送器的基本构架如下所示:

4.部分源码

`timescale 1ns / 1ps

module GPS_Rec(

i_clk,

i_rst,

i_QPSK,

i_BPSK,

//Capture

o_Ca_index,

o_CA,

o_abs_addCA,

o_P_index,

o_P,

o_abs_addP,

o_fre_est_Ca,

o_fre_est_P,

//Tracking

o_I_L1,

o_Q_L1,

o_I_L2,

o_Q_L2,

o_Dwen_rec_L1,

o_Dwen_rec_L2

);

input i_clk;

input i_rst;

input signed[15:0] i_QPSK;

input signed[15:0] i_BPSK;

//Capture

output [9:0] o_Ca_index;

output signed[1:0] o_CA;

output signed[21:0]o_abs_addCA;

output [10:0]o_P_index;

output signed[1:0] o_P;

output signed[23:0]o_abs_addP;

output signed[23:0]o_fre_est_Ca;

output signed[23:0]o_fre_est_P;

//Tracking

output signed[15:0]o_I_L1;

output signed[15:0]o_Q_L1;

output signed[15:0]o_I_L2;

output signed[15:0]o_Q_L2;

output signed[1:0] o_Dwen_rec_L1;

output signed[1:0] o_Dwen_rec_L2;

wire clk_ca;

wire clk_ca_2code;

wire clk_p;

wire clk_p_2code;

//2 time ca clock

CLOCK_DCM2 CLOCK_DCM2_u(

.i_clk (i_clk),

.i_rst (i_rst),

.o_clk_dwen (),

.o_clk_ca (clk_ca),

.o_clk_ca_2code (clk_ca_2code),

.o_clk_p (clk_p),

.o_clk_p_2code (clk_p_2code)

);

//CAPTURE

//CAPTURE

//frequency capture

wire signed[9:0] o_Ca_index;

wire signed[1:0] o_CA;

wire signed[21:0]o_abs_addCA;

frequency_capture_channel1 frequency_capture_channel1_u(

.i_clk (i_clk),

.i_clk_ca (clk_ca),

.i_clk_ca2times (clk_ca_2code),

.i_rst (i_rst),

.i_QPSK (i_QPSK),

.o_fre_est (o_fre_est_Ca),

.o_I_filter (),

.o_Q_filter (),

.o_Ca_index (o_Ca_index),

.o_CA (o_CA),

.o_abs_addIQ (o_abs_addCA)

);

wire signed[10:0] o_p_index;

wire signed[1:0] o_p;

wire signed[23:0] o_abs_addP;

frequency_capture_channel2 frequency_capture_channel2_u (

.i_clk (i_clk),

.i_clk_p (clk_p),

.i_clk_p2times (clk_p_2code),

.i_rst (i_rst),

.i_BPSK (i_BPSK),

.o_fre_est (o_fre_est_P),

.o_I_filter (),

.o_Q_filter (),

.o_p_index (o_P_index),

.o_p (o_P),

.o_abs_addIQ (o_abs_addP)

);

wire signed[15:0]o_I_filter1;

wire signed[15:0]o_Q_filter1;

wire signed[15:0]o_I_filter2;

wire signed[15:0]o_Q_filter2;

Frequency_track_tops Frequency_track_tops_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_QPSK (i_QPSK),

.i_BPSK (i_BPSK),

.i_FRE_index1(o_fre_est_Ca),

.i_FRE_index2(o_fre_est_P),

.o_I_filter1 (o_I_L1),

.o_Q_filter1 (o_Q_L1),

.o_I_filter2 (o_I_L2),

.o_Q_filter2 (o_Q_L2)

);

//CA capture

wire signed[1:0]Dwen_rec_L1;

CA_early_late_track_tops CA_early_late_track_tops_u(

.i_clk (clk_ca_2code),

.i_clk_ca (clk_ca),

.i_rst (i_rst),

.i_CA_index (o_Ca_index+1),

.i_Idin (o_I_L1),

.i_Qdin (o_Q_L1),

.o_dout (o_Dwen_rec_L1)

);

//P capture

wire signed[1:0]Dwen_rec_L2;

P_early_late_track_tops P_early_late_track_tops_u (

.i_clk (clk_p_2code),

.i_clk_p (clk_p),

.i_rst (i_rst),

.i_P_index (o_P_index+1),

.i_Idin (o_I_L2),

.i_Qdin (o_Q_L2),

.o_dout (o_Dwen_rec_L2)

);

endmodule

01_118m